Verilog HDL Statements

There are mainly two statments, function and always, in which the if-else and case (casex) can be used. There is another statement, initial, that is mainly used in the test bench for simulation, in which the if-else and case (casex) can be also used. Example: Design the following circuit with Verilog HDL statements.

Function statement

Function-case

The case can be used inside the function. Different from C, a "break" is not needed for each "case". If there are more things to be done within a "case", use "begin" and "end". The "default" is necessary because we must care about all the cases of "c" in the following codes.

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 |

module sw_7seg_led (

input [2:0] sw, // 3 switches

output [6:0] seven_seg_led // 7-segment LEDs

);

function [6:0] seg7; // no (); seg7 is function name

input [2:0] c; // input parameter

case (c) // case

3'd0 : seg7 = 7'b1000000; // 0's LED control, 0: light on

3'd1 : seg7 = 7'b1111001; // 1's LED control, 1: light off

3'd2 : seg7 = 7'b0100100; // 2's LED control

3'd3 : seg7 = 7'b0110000; // 3's LED control

3'd4 : seg7 = 7'b0011001; // 4's LED control

3'd5 : seg7 = 7'b0010010; // 5's LED control

default: seg7 = 7'b1111111; // default: all segments light off

endcase

endfunction

assign seven_seg_led = seg7(sw); // call function seg7. sw is corresponding to c of seg7

endmodule

|

Function-if-else

The if-else can be used inside the function. The "if-else" has a same grammar as C except using "begin" and "end" instead of "{" and "}".

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 |

module sw_7seg_led_if_else (

input [2:0] sw, // 3 switches

output [6:0] seven_seg_led // 7-segment LEDs

);

assign sw_7seg_led = seg7(sw); // sw is corresponding to c of seg7

function [6:0] seg7; // no (); seg7 is function name

input [2:0] c; // input parameter

if (c == 3'd0) seg7 = 7'b1000000; // 0's LED control, 0: light on

else if (c == 3'd1) seg7 = 7'b1111001; // 1's LED control, 1: light off

else if (c == 3'd2) seg7 = 7'b0100100; // 2's LED control

else if (c == 3'd3) seg7 = 7'b0110000; // 3's LED control

else if (c == 3'd4) seg7 = 7'b0011001; // 4's LED control

else if (c == 3'd5) seg7 = 7'b0010010; // 5's LED control

else seg7 = 7'b1111111; // default: all segments light off

endfunction

endmodule

|

Always statement

Always-case

The case can be used inside the always.

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 |

module sw_7seg_led_always_case (

input [2:0] sw, // 3 switches

output reg [6:0] seven_seg_led // 7-segment LEDs, will be combinational

);

always @* begin

case (sw) // case

3'd0 : seven_seg_led = 7'b1000000; // 0's LED control, 0: light on

3'd1 : seven_seg_led = 7'b1111001; // 1's LED control, 1: light off

3'd2 : seven_seg_led = 7'b0100100; // 2's LED control

3'd3 : seven_seg_led = 7'b0110000; // 3's LED control

3'd4 : seven_seg_led = 7'b0011001; // 4's LED control

3'd5 : seven_seg_led = 7'b0010010; // 5's LED control

default: seven_seg_led = 7'b1111111; // default: all segments light off

endcase

end

endmodule

|

Always-if-else

The if-else can be used inside the always.

1 2 3 4 5 6 7 8 9 10 11 12 13 14 |

module sw_7seg_led_always (

input [2:0] sw, // 3 switches

output reg [6:0] seven_seg_led // 7-segment LEDs, will be combinational

);

always @* begin

if (sw == 3'd0) seven_seg_led = 7'b1000000; // 0's LED control, 0: light on

else if (sw == 3'd1) seven_seg_led = 7'b1111001; // 1's LED control, 1: light off

else if (sw == 3'd2) seven_seg_led = 7'b0100100; // 2's LED control

else if (sw == 3'd3) seven_seg_led = 7'b0110000; // 3's LED control

else if (sw == 3'd4) seven_seg_led = 7'b0011001; // 4's LED control

else if (sw == 3'd5) seven_seg_led = 7'b0010010; // 5's LED control

else seven_seg_led = 7'b1111111; // default: all segments light off

end

endmodule

|

Test bench:

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 |

`timescale 1ns/1ns

module sw_7seg_led_always_tb;

reg [2:0] sw; // 3 switches

wire [6:0] seven_seg_led; // 7-segment LEDs, will be combinational

sw_7seg_led_always i0 (sw, seven_seg_led);

initial begin

#0 sw = 3'd0;

#8 $stop;

end

always #1 sw = sw + 3'd1;

endmodule

|

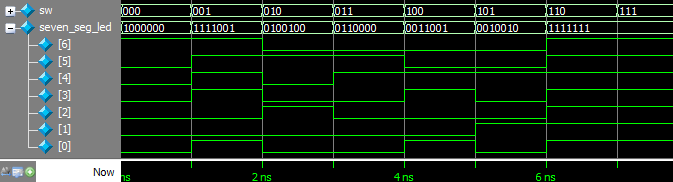

Waveform:

Exercise

-

Design the following circuit in Verilog HDL and implement it on FPGA (Display 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, a, b, c, d, e, f with seven-segment LED based on the 4-bit switch inputs).

module sw4_7seg_led ( input [3:0] sw, // 4 switches output [6:0] seven_seg_led // 7-segment LEDs, will be combinational ); assign seven_seg_led = seven_segments (sw); function [6:0] seven_segments; input [3:0] cnt; case(cnt) 4'h0 : seven_segments = 7'b1000000; 4'h1 : seven_segments = 7'b1111001; 4'h2 : seven_segments = 7'b0100100; 4'h3 : seven_segments = 7'b0110000; 4'h4 : seven_segments = 7'b0011001; 4'h5 : seven_segments = 7'b0010010; 4'h6 : seven_segments = ; 4'h7 : seven_segments = ; 4'h8 : seven_segments = 7'b0000000; 4'h9 : seven_segments = ; 4'ha : seven_segments = ; 4'hb : seven_segments = ; 4'hc : seven_segments = ; 4'hd : seven_segments = ; 4'he : seven_segments = ; 4'hf : seven_segments = ; endcase endfunction endmodulePin assignment:

set_location_assignment PIN_U13 -to sw[0] set_location_assignment PIN_V13 -to sw[1] set_location_assignment PIN_T13 -to sw[2] set_location_assignment PIN_T12 -to sw[3] set_location_assignment PIN_U21 -to seven_seg_led[0] set_location_assignment PIN_V21 -to seven_seg_led[1] set_location_assignment PIN_W22 -to seven_seg_led[2] set_location_assignment PIN_W21 -to seven_seg_led[3] set_location_assignment PIN_Y22 -to seven_seg_led[4] set_location_assignment PIN_Y21 -to seven_seg_led[5] set_location_assignment PIN_AA22 -to seven_seg_led[6]

- Implement the ALU of the previous exercise on FPGA and show the data with seven-segment LEDs (Use Function-Case and invoke the function 5 times for hex0 - hex4):

use switch 3,2,1,0 for a[3:0], and display on hex0 use switch 7,6,5,4 for b[3:0], and display on hex1 use switch 9,8 for aluc[1:0], and display on hex2 use led 3,2,1,0 for s[3:0], and display on hex3 use led 9 for z, and display on hex4

Invoke the function 5 times for hex0 - hex4 (function name: seven_segments):

module alu_7seg (a, b, aluc, s, z, hex0, hex1, hex2, hex3, hex4); input [3:0] a, b; input [1:0] aluc; output [6:0] hex0; // a output [6:0] hex1; // b output [6:0] hex2; // aluc output [6:0] hex3; // s output [6:0] hex4; // z output [3:0] s; output z; reg [3:0] s; assign z = ~|s; always @* begin case (aluc) 2'b00: s = a + b; 2'b01: s = ; 2'b10: s = ; 2'b11: s = ; endcase end assign hex0 = seven_segments (a); assign hex1 = seven_segments (b); assign hex2 = seven_segments ({2'b00,aluc}); assign hex3 = seven_segments (s); assign hex4 = seven_segments ({3'b000,z}); function [6:0] seven_segments; input [3:0] q; case (q) 'h0: seven_segments = 'b1000000; 'h1: seven_segments = 'b1111001; 'h2: seven_segments = 'b0100100; 'h3: seven_segments = 'b0110000; 'h4: seven_segments = 'b0011001; 'h5: seven_segments = 'b0010010; 'h6: seven_segments = ; 'h7: seven_segments = ; 'h8: seven_segments = 'b0000000; 'h9: seven_segments = ; 'ha: seven_segments = ; 'hb: seven_segments = ; 'hc: seven_segments = ; 'hd: seven_segments = ; 'he: seven_segments = ; 'hf: seven_segments = ; endcase endfunction endmodulePin assignment:

set_location_assignment PIN_U13 -to a[0] set_location_assignment PIN_V13 -to a[1] set_location_assignment PIN_T13 -to a[2] set_location_assignment PIN_T12 -to a[3] set_location_assignment PIN_AA15 -to b[0] set_location_assignment PIN_AB15 -to b[1] set_location_assignment PIN_AA14 -to b[2] set_location_assignment PIN_AA13 -to b[3] set_location_assignment PIN_AB13 -to aluc[0] set_location_assignment PIN_AB12 -to aluc[1] set_location_assignment PIN_AA2 -to s[0] set_location_assignment PIN_AA1 -to s[1] set_location_assignment PIN_W2 -to s[2] set_location_assignment PIN_Y3 -to s[3] set_location_assignment PIN_L1 -to z set_location_assignment PIN_U21 -to hex0[0] set_location_assignment PIN_V21 -to hex0[1] set_location_assignment PIN_W22 -to hex0[2] set_location_assignment PIN_W21 -to hex0[3] set_location_assignment PIN_Y22 -to hex0[4] set_location_assignment PIN_Y21 -to hex0[5] set_location_assignment PIN_AA22 -to hex0[6] set_location_assignment PIN_AA20 -to hex1[0] set_location_assignment PIN_AB20 -to hex1[1] set_location_assignment PIN_AA19 -to hex1[2] set_location_assignment PIN_AA18 -to hex1[3] set_location_assignment PIN_AB18 -to hex1[4] set_location_assignment PIN_AA17 -to hex1[5] set_location_assignment PIN_U22 -to hex1[6] set_location_assignment PIN_Y19 -to hex2[0] set_location_assignment PIN_AB17 -to hex2[1] set_location_assignment PIN_AA10 -to hex2[2] set_location_assignment PIN_Y14 -to hex2[3] set_location_assignment PIN_V14 -to hex2[4] set_location_assignment PIN_AB22 -to hex2[5] set_location_assignment PIN_AB21 -to hex2[6] set_location_assignment PIN_Y16 -to hex3[0] set_location_assignment PIN_W16 -to hex3[1] set_location_assignment PIN_Y17 -to hex3[2] set_location_assignment PIN_V16 -to hex3[3] set_location_assignment PIN_U17 -to hex3[4] set_location_assignment PIN_V18 -to hex3[5] set_location_assignment PIN_V19 -to hex3[6] set_location_assignment PIN_U20 -to hex4[0] set_location_assignment PIN_Y20 -to hex4[1] set_location_assignment PIN_V20 -to hex4[2] set_location_assignment PIN_U16 -to hex4[3] set_location_assignment PIN_U15 -to hex4[4] set_location_assignment PIN_Y15 -to hex4[5] set_location_assignment PIN_P9 -to hex4[6]