#### 論理回路入門(12)

順序回路3:交通信号機制御システム設計

李 亜民

2024年12月10日(火)

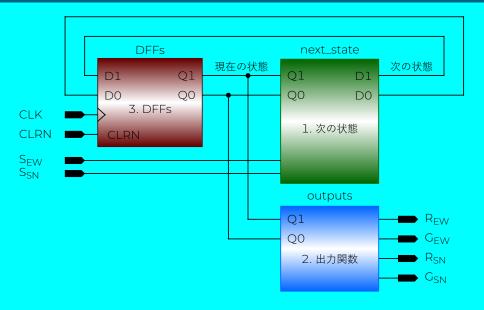

# 順序回路

#### ポイント

- 順序回路の基本構造

- 順序回路の分析

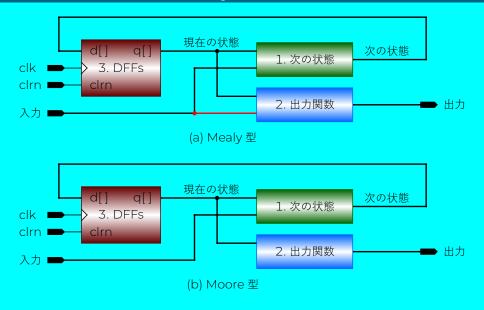

- Mealy 型と Moore 型順序回路

- 順序回路設計の手順

- 状態遷移図

- 次の状態の真理値表、論理式、および回路

- 出力関数の真理値表、論理式、および回路

- 交通信号機制御システム

### 論理回路の種類

組み合わせ回路 (Combinational Circuit): 現在の入力のみで出力が決まる回路である。

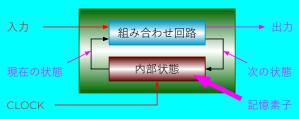

順序回路 (Sequential Circuit): 内部状態と入力信号で 出力が決まる回路である。有限状態機械 (Finite state machine — FSM) とも呼ばれる。

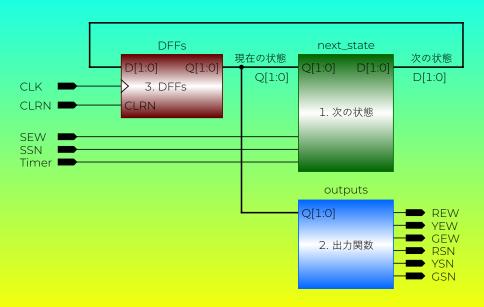

## 順序回路 — Mealy 型と Moore 型

#### 順序回路設計の手順

- 📵 問題を理解する。

- ② 状態遷移図をつくる。

- ⑤ FF の数を決める (n = [log₂N]、N は状態の数)。

- ④ 各状態にnビットの番号を付け、真理値表をつくる。

- ▶ 次の状態の真理値表をつくる。

- ▶ 出力関数の真理値表をつくる。

- ◎ 真理値表から論理式をつくる (どの条件で出力が 1 になるか)。

- ▶ カルノー図を用いて論理式を簡単化する。

- ◎ 論理式から回路をつくる。

- アストベンチをつくる (シミュレーションするため)。

- 📵 回路をシミュレーションする (回路設計の正当性検証)。

- ◎ 与えられた回路の動作を理解する (波形の説明)。

## 順序回路の設計(問題と状態遷移図)

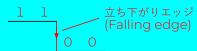

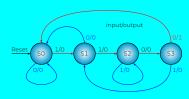

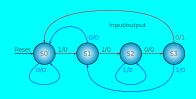

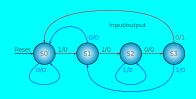

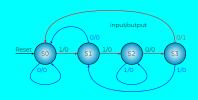

問題:入力信号が1ビットで、入力列が"1100"の場合に1を出力する(立ち下がりエッジ検出)順序回路を設計せよ。

# 順序回路の設計(問題と状態遷移図)

問題:入力信号が1ビットで、入力列が"1100"の場合に1を出力する(立ち下がりエッジ検出)順序回路を設計せよ。

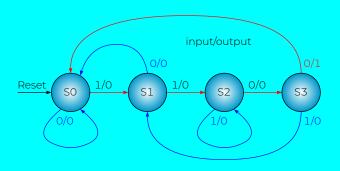

#### 状態遷移図:

|    | 現在の状態 |      | 入力 | 次の状態      | 出力 |

|----|-------|------|----|-----------|----|

|    | q[1]  | q[0] | С  | d[1] d[0] | r  |

| S0 | 0     | 0    | 0  |           |    |

| 現在の状態 |      | 入力   |   | 次の状態 |      |      |   |

|-------|------|------|---|------|------|------|---|

|       | q[1] | q[0] | С |      | d[1] | d[0] | r |

| SO    | 0    | 0    | 0 | S0   | 0    | 0    | 0 |

|       |      |      | 1 |      |      |      |   |

| 現在の状態 |      | 入力   | 次の状態 |    |      | 出力   |   |

|-------|------|------|------|----|------|------|---|

|       | q[1] | q[0] | С    |    | d[1] | d[0] | r |

| SO    | 0    | 0    | 0    | S0 | 0    | 0    | 0 |

|       |      |      | 1    | Sl | 0    | 1    | 0 |

| Sl    | 0    | 1    | 0    |    |      |      |   |

| 現在の状態 |      |      | 入力 | 次の状態 |      |      | 出力 |

|-------|------|------|----|------|------|------|----|

|       | q[1] | q[0] | С  |      | d[1] | d[0] | r  |

| SO    | 0    | 0    | 0  | S0   | 0    | 0    | 0  |

|       |      |      | 1  | Sl   | 0    | 1    | 0  |

| Sl    | 0    | 1    | 0  | SO   | 0    | 0    | 0  |

|       |      |      | 1  |      |      |      |    |

| 現在の状態 |      | 入力   | 次の状態 |    |      | 出力   |   |

|-------|------|------|------|----|------|------|---|

|       | q[1] | q[0] | С    |    | d[1] | d[0] | r |

| SO    | 0    | 0    | 0    | S0 | 0    | 0    | 0 |

|       |      |      | 1    | Sl | 0    | 1    | 0 |

| Sl    | 0    | 1    | 0    | SO | 0    | 0    | 0 |

|       |      |      | 1    | S2 | 1    | 0    | 0 |

| S2    | 1    | 0    | 0    |    |      |      |   |

| 現在の状態 |      |      | 入力 | 次の状態 |      |      | 出力 |

|-------|------|------|----|------|------|------|----|

|       | q[1] | q[0] | С  |      | d[1] | d[0] | r  |

| SO    | 0    | 0    | 0  | S0   | 0    | 0    | 0  |

|       |      |      | 1  | Sl   | 0    | 1    | 0  |

| Sl    | 0    | 1    | 0  | S0   | 0    | 0    | 0  |

|       |      |      | 1  | S2   | 1    | 0    | 0  |

| S2    | 1    | 0    | 0  | S3   | 1    | 1    | 0  |

|       |      |      | 1  |      |      |      |    |

|    | 現在の状態 |      | 入力 | 次の状態 |      |      | 出力 |

|----|-------|------|----|------|------|------|----|

|    | q[1]  | q[0] | С  |      | d[1] | d[0] | r  |

| SO | 0     | 0    | 0  | S0   | 0    | 0    | 0  |

|    |       |      | 1  | Sl   | 0    | 1    | 0  |

| Sl | 0     | 1    | 0  | SO   | 0    | 0    | 0  |

|    |       |      | 1  | S2   | 1    | 0    | 0  |

| S2 | 1     | 0    | 0  | S3   | 1    | 1    | 0  |

|    |       |      | 1  | S2   | 1    | 0    | 0  |

| S3 | 1     | 1    | 0  |      |      |      |    |

| 現在の状態 |      | 入力   | 次の状態 |    |      | 出力   |   |

|-------|------|------|------|----|------|------|---|

|       | q[1] | q[0] | С    |    | d[1] | d[0] | r |

| SO    | 0    | 0    | 0    | S0 | 0    | 0    | 0 |

|       |      |      | 1    | Sl | 0    | 1    | 0 |

| Sl    | 0    | 1    | 0    | SO | 0    | 0    | 0 |

|       |      |      | 1    | S2 | 1    | 0    | 0 |

| S2    | 1    | 0    | 0    | S3 | 1    | 1    | 0 |

|       |      |      | 1    | S2 | 1    | 0    | 0 |

| S3    | 1    | 1    | 0    | SO | 0    | 0    | 1 |

|       |      |      | 1    |    |      |      |   |

|    | 現在の状態 | 影    | 入力 |    | 次の状態 |      |   |

|----|-------|------|----|----|------|------|---|

|    | q[1]  | q[0] | С  |    | d[1] | d[0] | r |

| SO | 0     | 0    | 0  | S0 | 0    | 0    | 0 |

|    |       |      | 1  | Sl | 0    | 1    | 0 |

| Sl | 0     | 1    | 0  | SO | 0    | 0    | 0 |

|    |       |      | 1  | S2 | 1    | 0    | 0 |

| S2 | 1     | 0    | 0  | S3 | 1    | 1    | 0 |

|    |       |      | 1  | S2 | 1    | 0    | 0 |

| S3 | 1     | 1    | 0  | SO | 0    | 0    | 1 |

|    |       |      | 1  | S1 | 0    | 1    | 0 |

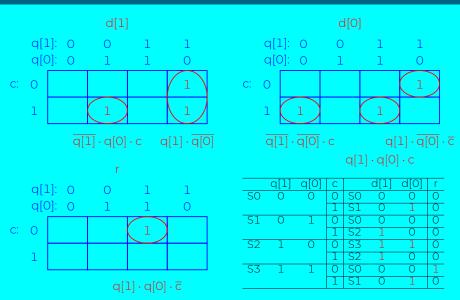

#### 順序回路の設計(カルノー図)

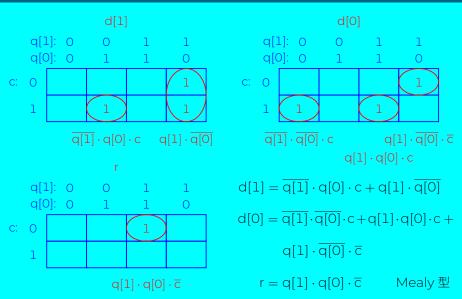

# 順序回路の設計(カルノー図と論理式)

# 順序回路の設計(論理式と回路図)

$$\begin{split} d[1] &= \overline{q[1]} \cdot q[0] \cdot c + q[1] \cdot \overline{q[0]} \\ d[0] &= \overline{q[1]} \cdot \overline{q[0]} \cdot c + q[1] \cdot q[0] \cdot c + q[1] \cdot \overline{q[0]} \cdot \overline{c} \\ r &= q[1] \cdot q[0] \cdot \overline{c} \end{split}$$

## 順序回路の設計(回路)

```

module detector (clk, clrn, c, r);

input clk, clrn, c;

output r;

reg [1:0] q; // current state

wire [1:0] d; // next state

// 1. next state -----

assign d[1] = q[1] & q[0] & c | q[1] & q[0];

assign d[0] = q[1] & q[0] & c | q[1] & q[0] & c |

q[1] & ~q[0] & ~c;

assign r = q[1] & q[0] & c;

// 2. outputs ----- 2

assign r = q[1] & q[0] & c: // S3 & c

// 3. dffs ----- 3

always @(posedge clk or negedge clrn) begin // dffs

if (clrn == 0) begin

a \le 0:

end else begin

q <= d:

end

end

endmodule

```

'timescale 1ns/1ns

#### 順序回路の設計(テストベンチ)

```

'timescale 1ns/1ns

module detector tb:

reg clk, clrn, a, x;

wire r;

detector i0 (clk, clrn, x, r):

initial begin

#0 clk = 1; clrn = 0; x = 0; // S0

#1 clrn = 1:

#4 x = 1:

#4 x = 0:

#4 x = 1:

#2 x = 0:

#2 x = 1:

\#6 \quad x = 0:

#4 x = 1:

#4 x = 0:

#2 x = 1:

#4 x = 0:

#8 $finish:

end

always #1 clk = ~clk:

initial begin

$dumpfile ("detector.vcd");

$dumpvars:

end

endmodule

detector_tb.v

```

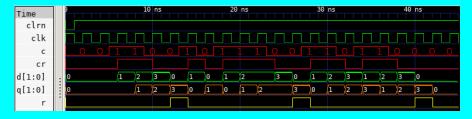

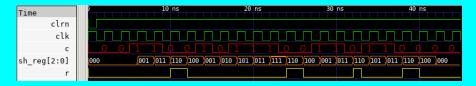

# 順序回路の設計(波形)

- % iverilog -Wall -o detector detector\_tb.v detector.v

- % vvp detector

- % gtkwave detector.vcd

c = 0011001011100110110000 注意: 間違った波形

MAC対応: ターミナルで gtkwave 起動後 SST の detector\_tb の左側にある三角形のボタンを押し、表示された iO を選択することで機械の中の信号も全て摘出できる。

Windows/ModelSim 対応: add wave -r /\*

#### 順序回路の設計(回路)

```

'timescale 1ns/1ns

module detector (clk. clrn. c. r):

input clk, clrn, c;

output r;

reg [1:0] q; // current state

wire [1:0] d; // next state

// 1. next state -----

assign d[1] = q[1] & q[0] & c | q[1] & q[0];

assign d[0] = q[1] & q[0] & c | q[1] & q[0] & c |

q[1] & ~q[0] & ~c;

assign r = q[1] & q[0] & c;

// 2. outputs ----- 2

assign r = q[1] & q[0] & c : // S3 & c

// 3. dffs ----- 3

always @(posedge clk or negedge clrn) begin // dffs

if (clrn == 0) begin

a \le 0:

end else begin

q <= d:

end

end

detector.v

endmodule

```

```

'timescale 1ns/1ns

module det_reg (clk, clrn, c, r);

input clk, clrn, c;

output r;

reg cr; // registered c

reg [1:0] q; // current state

wire [1:0] d; // next state

// 1. next state -----

assign d[1] = q[1] & q[0] & cr | q[1] & q[0];

assign d[0] = q[1] & q[0] & cr | q[1] & q[0] & cr |

q[1] & ~q[0] & ~cr;

assign r = q[1] & q[0] & cr;

// 2. outputs ----- 2

assign r = q[1] & q[0] & ~cr: // S3 & ~cr

// 3. dffs ----- 3

always @(posedge clk or negedge clrn) begin // dffs

if (clrn == 0) begin

q <= 0; cr <= 0;

end else begin

q <= d; cr <= c; // registering c

end

end

det_req.v

endmodule

```

```

'timescale 1ns/1ns

module det reg tb:

reg clk, clrn, a, x;

wire r;

det_reg i0 (clk, clrn, x, r);

initial begin

#0 clk = 1; clrn = 0; x = 0; // S0

#1 clrn = 1:

#4 x = 1:

#4 x = 0:

#4 x = 1:

#2 x = 0;

#2 x = 1:

\#6 \quad x = 0:

#4 x = 1:

#4 x = 0:

#2 x = 1:

#4 x = 0:

#8 $finish:

end

always #1 clk = ~clk:

initial begin

$dumpfile ("det_reg.vcd");

$dumpvars:

end

endmodule

det_reg_tb.v

```

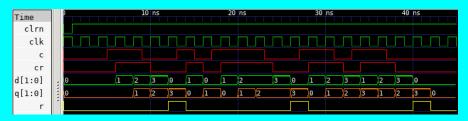

- % iverilog -Wall -o det\_reg det\_reg\_tb.v det\_reg.v

- % vvp det\_reg

- % gtkwave det\_reg.vcd

c = 0011001011100110110000

cr:同期されたc

間違った波形が生成されてなかった(入力を同期した)

#### 入力 c 同期波形 (cr を使用)

#### 入力c非同期波形(cを使用)

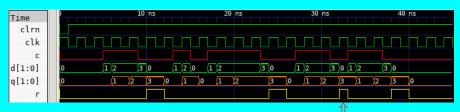

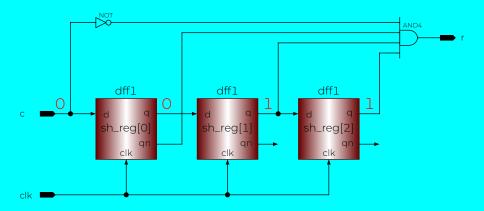

パターン検出は シフトレジスタで 実現可能である

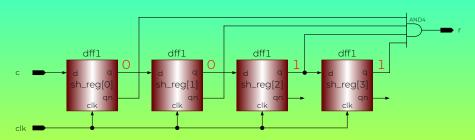

#### "1100"のパターンを検出する回路

```

'timescale 1ns/1ns

module det_sh (clk, clrn, c, r);

input clk, clrn, c;

output r;

reg [2:0] sh_reg; // 3-bit register

// dffs

always @(posedge clk or negedge clrn) begin // dffs

if (clrn == 0) begin

sh reg <= 0:

end else begin

// shift 3-bit register

sh_reg[2] <= sh_reg[1];

sh_reg[1] <= sh_reg[0];

sh reg[0] <= c:

end

dff1

dff1

dffl

end

// outputs

assign r = sh_reg[2] & // 1

sh_reg[1] & // 1

~sh_reg[0] & // 0

~c:

det_sh.v

endmodule

```

```

'timescale 1ns/1ns

module det sh tb:

reg clk, clrn, a, x;

wire r;

det sh i0 (clk, clrn, x, r):

initial begin

#0 clk = 1; clrn = 0; x = 0; // S0

#1 clrn = 1:

#4 x = 1:

#4 x = 0:

#4 x = 1:

#2 x = 0;

#2 x = 1:

\#6 \quad x = 0:

#4 x = 1:

#4 x = 0:

#2 x = 1:

#4 x = 0:

#8 $finish:

end

always #1 clk = ~clk:

initial begin

$dumpfile ("det_sh.vcd");

$dumpvars:

det_sh_tb.v

end

endmodule

```

- % iverilog -Wall -o det\_sh det\_sh\_tb.v det\_sh.v

- % vvp det\_sh

- % gtkwave det\_sh.vcd

#### 比較: detector 回路の波形

発展:4ビット DFF を使用して"1100"パターンを検出する回路を設計してください(入力を同期する)。

立ち下がりエッジ検出については、PS2 キーボード インターフェース コントローラー回路 ps2\_keyboard.v を参照してください。

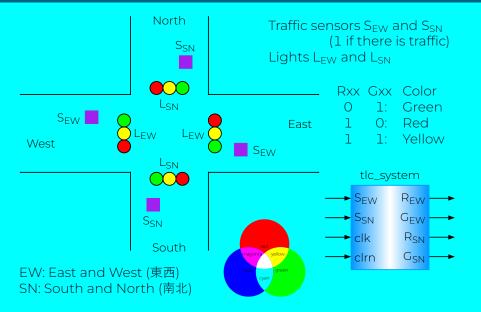

# 交通信号機 制御システム

## 交通信号機制御システム(問題)

# 交通信号機制御(回路)

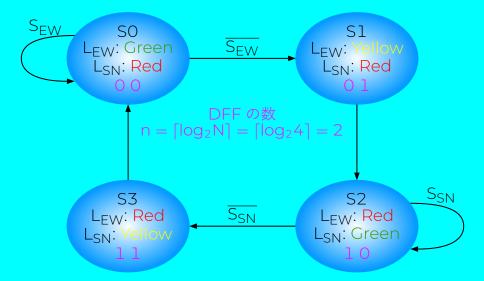

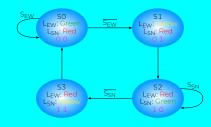

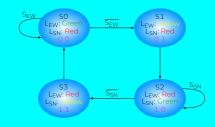

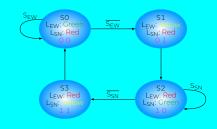

#### 交通信号機制御(状態遷移図)

| 3  | 現在の状態 |    | 入               | 力               | 次の状態  |  |  |

|----|-------|----|-----------------|-----------------|-------|--|--|

|    | Q1    | Q0 | S <sub>EW</sub> | S <sub>SN</sub> | D1 D0 |  |  |

| SO | 0     | 0  | 0               | Χ               |       |  |  |

|    | 現在の状態 |    | 入               | 入力              |    | 次の状態 |    |  |

|----|-------|----|-----------------|-----------------|----|------|----|--|

|    | Q1    | Q0 | S <sub>EW</sub> | S <sub>SN</sub> |    | D1   | D0 |  |

| SC | 0     | 0  | 0               | Χ               | Sl | 0    | 1  |  |

|    |       |    | 1               | Χ               |    |      |    |  |

|    | 現在の状態 |    | 入力              |                 | 次の状態 |    |    |

|----|-------|----|-----------------|-----------------|------|----|----|

|    | Q1    | Q0 | S <sub>EW</sub> | S <sub>SN</sub> |      | D1 | D0 |

| SO | 0     | 0  | 0               | Χ               | Sl   | 0  | 1  |

|    |       |    | 1               | X               | S0   | 0  | 0  |

| Sl | 0     | 1  | Χ               | Χ               |      |    |    |

|    | 現在の状態 |    | 入力              |          | 次の状態 |    |    |

|----|-------|----|-----------------|----------|------|----|----|

|    | Q1    | Q0 | S <sub>EW</sub> | $S_{SN}$ |      | Dl | D0 |

| SO | 0     | 0  | 0               | Χ        | Sl   | 0  | 1  |

|    |       |    | 1               | Х        | S0   | O  | 0  |

| Sl | 0     | 1  | Х               | X        | S2   | 1  | 0  |

| S2 | 1     | 0  | Χ               | 0        |      |    |    |

|    | 現在の状態 |    | 入力              |                 | 次の状態 |    |    |

|----|-------|----|-----------------|-----------------|------|----|----|

|    | Q1    | Q0 | S <sub>EW</sub> | S <sub>SN</sub> |      | Dl | D0 |

| SO | 0     | 0  | 0               | Χ               | Sl   | 0  | 1  |

|    |       |    | 1               | Х               | S0   | 0  | 0  |

| Sl | 0     | 1  | X               | X               | S2   | 1  | 0  |

| S2 | 1     | 0  | X               | 0               | S3   | 1  | 1  |

|    |       |    | X               | 1               |      |    |    |

| 3  | 現在の状態 |    | 入               | 入力       |    | 次の状態 |    |  |

|----|-------|----|-----------------|----------|----|------|----|--|

|    | Q1    | Q0 | S <sub>EW</sub> | $S_{SN}$ |    | D1   | D0 |  |

| SO | 0     | 0  | 0               | Χ        | Sl | 0    | 1  |  |

|    |       |    | 1               | Х        | S0 | 0    | 0  |  |

| Sl | 0     | 1  | Х               | X        | S2 | 1    | 0  |  |

| S2 | 1     | 0  | Χ               | 0        | S3 | 1    | 1  |  |

|    |       |    | X               | 1        | S2 | 1    | 0  |  |

| S3 | 1     | 1  | Χ               | Χ        |    |      |    |  |

|    | 現在の状態 |    | 入力              |                 | 次の状態 |    |    |

|----|-------|----|-----------------|-----------------|------|----|----|

|    | Q1    | Q0 | S <sub>EW</sub> | S <sub>SN</sub> |      | D1 | D0 |

| SO | 0     | 0  | 0               | Χ               | Sl   | 0  | 1  |

|    |       |    | 1               | Х               | S0   | 0  | 0  |

| S1 | 0     | 1  | Х               | X               | S2   | 1  | 0  |

| S2 | 1     | 0  | Χ               | 0               | S3   | 1  | 1  |

|    |       |    | Х               | 1               | S2   | 1  | 0  |

| S3 | 1     | 1  | X               | Χ               | S0   | 0  | 0  |

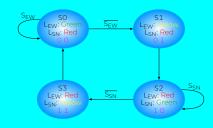

# 交通信号機制御(次の状態の論理式)

| Ţ. | 現在の状態 |    | 入力              |                 | 次の状態 |    |    |

|----|-------|----|-----------------|-----------------|------|----|----|

|    | Q1    | Q0 | S <sub>EW</sub> | S <sub>SN</sub> |      | Dl | D0 |

| SO | 0     | 0  | 0               | Χ               | Sl   | 0  | 1  |

|    |       |    | 1               | Χ               | S0   | 0  | 0  |

| Sl | 0     | 1  | Х               | Χ               | S2   | 1  | 0  |

| S2 | 1     | O  | Χ               | 0               | S3   | 1  | 1  |

|    |       |    | X               | 1               | S2   | 1  | 0  |

| S3 | 1     | 1  | Χ               | Χ               | S0   | Ο  | 0  |

次の状態の論理式

$$D1 = \overline{Q1} \cdot Q0 + Q1 \cdot \overline{Q0}$$

$$D0 = \overline{Q1} \cdot \overline{Q0} \cdot \overline{S}_{EW} + Q1 \cdot \overline{Q0} \cdot \overline{S}_{SN}$$

| S <sub>SN</sub> 00 | 1 | 1 |

|--------------------|---|---|

| 01                 | 1 | 1 |

| 11                 | 1 | 1 |

| 10                 | 1 | 1 |

|                                 |          |   | D      |   |            |

|---------------------------------|----------|---|--------|---|------------|

| Ç                               | 01<br>00 | 0 | 0<br>1 | 1 | 1<br>0     |

| <sub>EW</sub> S <sub>SN</sub> ( | 00       | 1 |        |   | 1          |

| C                               | 1        | 1 |        |   |            |

| 1                               | 1        |   |        |   |            |

| 1                               | 0        |   |        |   | $\sqrt{1}$ |

SFW

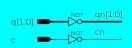

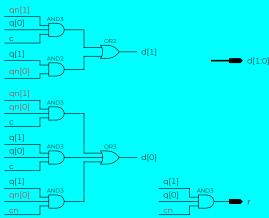

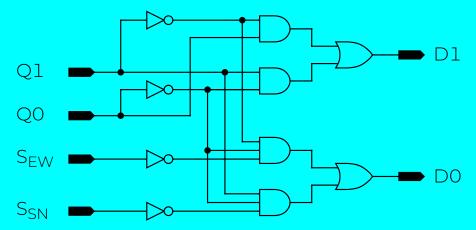

# 交通信号機制御(次の状態の回路)

$$D1 = \overline{Q1} \cdot Q0 + Q1 \cdot \overline{Q0}$$

$$D0 = \overline{Q1} \cdot \overline{Q0} \cdot \overline{S_{EW}} + Q1 \cdot \overline{Q0} \cdot \overline{S_{SN}}$$

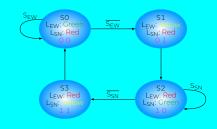

### 交通信号機制御(出力関数の真理値表)

出力関数の真理値表

Color encoding: R G Color

0 1: Green 1 0: Red

S0: L<sub>EW</sub>: Green; L<sub>SN</sub>: Red S1: L<sub>EW</sub>: Yellow; L<sub>SN</sub>: Red

1 1: Yellow

S2: L<sub>EW</sub>: Red; L<sub>SN</sub>: Green S3: L<sub>FW</sub>: Red; L<sub>SN</sub>: Yellow

| 刊  | 現在の状態 |    |                 | 出力              |          |                 |  |  |

|----|-------|----|-----------------|-----------------|----------|-----------------|--|--|

|    | Ql    | Q0 | R <sub>EW</sub> | G <sub>EW</sub> | $R_{SN}$ | G <sub>SN</sub> |  |  |

| SO | 0     | 0  | 0               | 1               | 1        | 0               |  |  |

| Sl | 0     | 1  | 1               | 1               | 1        | 0               |  |  |

| S2 | 1     | 0  | 1               | 0               | 0        | 1               |  |  |

| S3 | 1     | 1  | 1               | 0               | 1        | 1               |  |  |

### 交通信号機制御(出力関数の論理式)

|    | 現在の状態 |    |                 | 出力              |          |                 |  |  |

|----|-------|----|-----------------|-----------------|----------|-----------------|--|--|

|    | Ql    | Q0 | R <sub>EW</sub> | G <sub>EW</sub> | $R_{SN}$ | G <sub>SN</sub> |  |  |

| SO | 0     | 0  | 0               | 1               | 1        | 0               |  |  |

| Sl | 0     | 1  | 1               | 1               | 1        | 0               |  |  |

| S2 | 1     | 0  | 1               | 0               | 0        | 1               |  |  |

| S3 | 1     | 1  | 1               | 0               | 1        | 1               |  |  |

#### 出力関数の論理式

## 交通信号機制御(出力関数の回路)

$$R_{EW} = Q1 + Q0$$

$$G_{EW} = \overline{Q1}$$

$$R_{SN} = \overline{Q1} + Q0$$

$$G_{SN} = Q1$$

$$wire$$

$$Q1$$

$$Q0$$

$$R_{EW}$$

$$R_{SN}$$

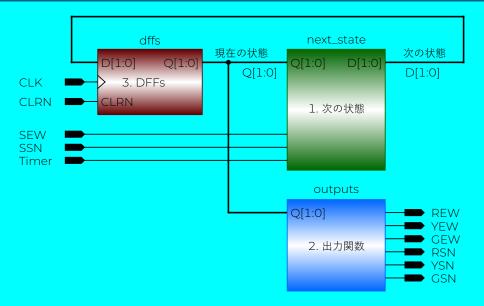

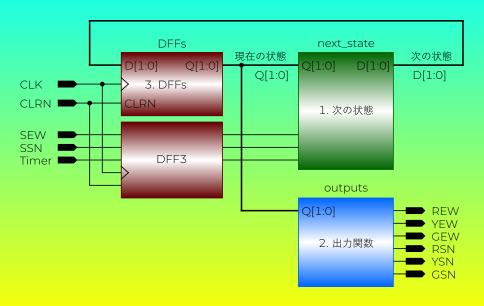

## 交通信号機制御(回路)

```

'timescale 1ns/1ns

module tlc_system (CLK, CLRN, SEW, SSN, REW, GEW, RSN, GSN);

input CLK, CLRN, SEW, SSN;

output REW, GEW, RSN, GSN; // outputs

assign D[1] = {}^{\sim}Q[1] \& Q[0] | Q[1] \& {}^{\sim}Q[0];

assign D[0] = {}^{\circ}Q[1] & {}^{\circ}Q[0] & {}^{\circ}SEW | Q[1] & {}^{\circ}Q[0] & {}^{\circ}SSN;

// 2. outputs ----- 2

assign REW = Q[1] | Q[0];  \begin{array}{cccc} R_{EW} = Q1 + Q0 \\ assign GEW = ~Q[1]; & G_{EW} = \overline{Q1} \\ assign RSN = ~Q[1] + Q[0]; & R_{SN} = \overline{Q1} + Q0 \\ \end{array}

always @(posedge CLK or negedge CLRN) begin // DFFs

if (CLRN == 0) begin

Q <= 0;

end else begin

Q \leq D:

end

end

tlc system.v

endmodule

```

### 交通信号機制御(テストベンチ)

```

'timescale 1ns/1ns

module tlc_system_tb;

reg CLK, CLRN, SEW, SSN;

wire REW, GEW, RSN, GSN:

tlc_system iO (CLK, CLRN, SEW, SSN, REW, GEW, RSN, GSN);

initial begin

#0 CLK = 1: CLRN = 0: SEW = 1: SSN = 0:

#1 CLRN = 1:

#4 SEW = 0:

#2 SSN = 1:

#4 SSN = 0:

#22 $finish;

end

always #1 CLK = ~CLK:

initial begin

$dumpfile ("tlc_system.vcd");

$dumpvars:

end

tlc_system_tb.v

endmodule

```

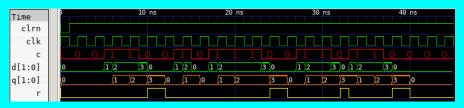

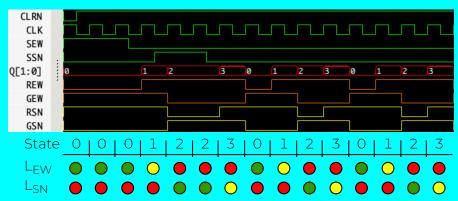

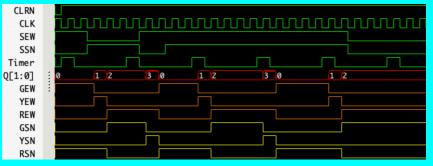

# 交通信号機制御(波形)

- % iverilog -Wall -o tlc\_system tlc\_system\_tb.v tlc\_system.v

- % vvp tlc\_system

- % gtkwave tlc\_system.vcd

この回路では、どの方向からも車が来ないとき、信号機の色が変わり続けたり、一方から車が来続けると、 たとえもう一方に多くの車があってもずっと信号が変わらなかったりするという問題があった。

#### 順序回路設計の手順

- 📵 問題を理解する。

- ② 状態遷移図をつくる。

- ⑤ FF の数を決める (n = [log₂N]、N は状態の数)。

- 個 各状態にnビットの番号を付け、真理値表をつくる。

- ▶ 次の状態の真理値表をつくる。

- ▶ 出力関数の真理値表をつくる。

- ◎ 真理値表から論理式をつくる (どの条件で出力が 1 になるか)。

- ▶ カルノー図を用いて論理式を簡単化する。

- ◎ 論理式から回路をつくる。

- プテストベンチをつくる (シミュレーションするため)。

- 📵 回路をシミュレーションする (回路設計の正当性検証)。

- ❷ 与えられた回路の動作を理解する(波形の説明)。

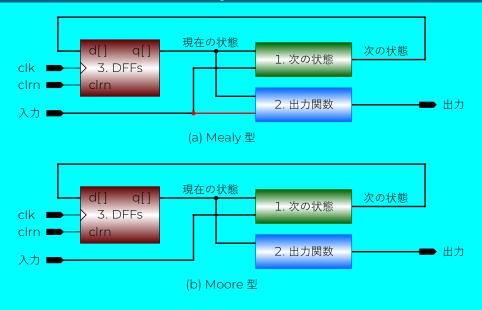

# 順序回路 — Mealy 型と Moore 型

# 順序回路のまとめ

#### まとめ

- 順序回路の基本構造

- 順序回路の分析

- Mealy 型と Moore 型順序回路

- 順序回路設計の手順

- 状態遷移図

- 次の状態の真理値表、論理式、および回路

- 出力関数の真理値表、論理式、および回路

- 交通信号機制御システム

交通信号機制御システムを設計し動作検証シミュレーションして下さい。

tlc

SEW REW YEW SSN YEW GEW SN: 南北 G: 緑信号 (1: 点灯; 0: 消灯) GEW SN: 南北 G: 緑信号 (1: 点灯; 0: 消灯) Timer RSN SN: 南北 G: 緑信号 (1: 点灯; 0: 消灯) Timer = 1: SEW = SSN = 1 (東西と南北車がある) 会 状態遷移を有効にする。

Timer = 0: SEW = SSN = 1 (東西と南北車がある) 会 状態遷移を無効にする (維持する)。

状態の割り当ては P46 の波形を参照してください。注意事項:

- (1) もし SEW = SSN = 0, 状態変化なし (Timer: ドントケア)

- (2) もし SEW ≠ SSN, 状態遷移を有効にする (Timer: ドントケア)

- (3) もし SEW = SSN = 1 かつ Timer = 1, 状態遷移を有効にする

- (4) もし SEW = SSN = 1 かつ Timer = 0, 状態遷移を無効にする

モジュール名は <u>tlc.v</u> にすること。 テストベンチ tlc\_tb.v を使って下さい。

レポートの必須項目:

(1) 状態遷移図

- (2) 次の状態 next\_state の真理値表

- (3) 次の状態 next\_state 各出力信号のカルノー図

- (4) 次の状態 next\_state の論理式

D[1] =

D[0] =

(5) 次の状態 next\_state の回路図

- (6) 出力関数 outputs の真理値表

- (7) 出力関数 outputs 各出力信号のカルノー図

- (8) 出力関数 outputs の論理式

```

REW =

```

YEW =

GFW =

RSN =

YSN =

GSN =

(9) 出力関数 outputs の回路図

```

'timescale 1ns/1ns

module tlc (CLK, CLRN, SEW, SSN, Timer, REW, YEW, GEW, RSN, YSN, GSN);

input CLK, CLRN, SEW, SSN, Timer;

output REW, YEW, GEW, RSN, YSN, GSN;

reg [1:0] Q; // current state

wire [1:0] D; // next state

// 1. next state ----- 1

assign D[1] = ;

assign D[0] = ;

// 2. outputs ----- 2

assign REW = ;

assign YEW = :

assign GEW = :

assign RSN = :

assign YSN = :

assign GSN = :

// 3. DFFs ----- 3

always @(posedge CLK or negedge CLRN) begin // DFFs

if (CLRN == 0) begin

Q \ll 0;

end else begin

Q \leq D:

end

end

tlc.v

endmodule

```

% iverilog -Wall -o tlc tlc\_tb.v tlc.v

% vvp tlc

% gtkwave tlc.vcd

波形を説明してください。

Timer = 0, 維持する

tlc\_tb.v

MAC 対応: ターミナルで gtkwave 起動後 SST の tlc\_tb の左側にある三角形のボタンを押し、表示された iO を選択することで機械の中の信号も全て摘出できる。 Windows/ModelSim 対応: add wave -r /\*

#### 発展:入力を同期する

#### 入力を同期しない