### 論理回路入門(1)

論理回路基礎1:論理演算と論理ゲート

李 亜民

2024年9月24日(火)

### 論理回路入門

#### 授業の内容

- <mark>論理回路の基本</mark>: ブール代数、真理値表、カルノー図、論 理式の積和形と和積形、回路の設計と動作検証の方法

- 組合せ回路: 半加算器、全加算器、リップルキャリーア ダー、キャリールックアヘッドアダー、ツリー型桁上げ 先見加算器、加算器を利用した減算器、マルチプレクサ、 7セグメント LED、ALU、デコーダ、エンコーダ

- 順序回路: RS ラッチ、D ラッチ、D フリップフロップ、T フリップフロップ、JK フリップフロップ、レジスタ・ ファイル、状態遷移図、交通信号機制御システム、N 進 カウンター

### 論理回路入門

- 成績評価

課題レポート成績 × 60% +

期末試験成績 × 40% (期末試験: 参照不可)

- 課題レポートの提出:次回の授業開始前までに いかなる理由でも遅延提出は認めない(遅刻厳禁) 課題レポートの提出:学習支援システム(Hoppii)

- 教科書: 授業のスライドの PDF ファイル

- 参考書: ディジタル回路設計とコンピュータアーキテクチャ第2版2017

- その他: ノート PC をクラスに持ち込んでください

### 論理回路入門

#### 回路の設計と動作検証の方法について

- C言語でソフトウェアを開発する場合、Cプログラムを コンパイルするためにCコンパイラが必要である。コン パイルされたプログラムを実行して、期待通りの結果が 得られるかどうかを確認する。

- 同様に、設計した回路が期待通りの結果を出せるかどう かを検証することも必要である。

- 検証する方法はいくつかある。たとえば、Xilinx ISE / Vivado、Intel Quartus / ModelSim などである。ただし、これらのツールは M1 Mac PC では実行できない。

- この講義では、Verilog HDLを使用して論理回路を実装する。講義スライドでは、Verilog HDL 回路の例とすべての検証用のテストベンチを用意する。

今日のポイント

### 論理演算と論理ゲート

#### ポイント

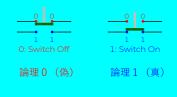

- 0と1の表現(電圧の低/高)

- 論理演算と論理ゲート

- ▶ 基本的な論理演算と論理ゲート: AND、OR、NOT

- ▶ ほかのゲート: NAND、NOR、XOR、XNOR

- 論理演算の理解(電球を点灯する回路)

- 真理値表、論理式と論理回路

- ハードウェア記述言語

- Verilog HDL (Hardware Description Language)

- シミュレーションのためのテストベンチ (Test bench)

- iverilog と gtkwave

### 論理回路とは

- 論理回路は論理演算を行う電気回路である。

- デジタル回路とも呼ばれる。

- 論理回路を使う場所

- ▶ コンピューター、携帯電話、ゲーム機

- ▶ テレビ、DVD レコーダー、デジタルカメラ

- ▶ 人工衛星、ナビゲーション

- ▶ 冷蔵庫、洗濯機、電子レンジ

- ▶ コピー機、プリンタ

- ■電卓、時計、リモコン

- ▶ 自動運転車、・・・・・・・

### 論理演算とは

- コンピュータのハードウェアは、電圧の高/低または電 圧の有/無の状態を動作の基本としている。

- これら二つの状態を数値化して表現するには、1と0の 二つの数値を組み合わせる2進数が最適である。

- コンピュータでは、電圧が高いまたは電圧がある状態を2進数の1に、電圧が低いまたは電圧が無い状態を2進数の0に割り当てている。

- 2進数は10進数と同じような四則演算(和、差、積、商) のほかに、2進数特有な論理演算がある。

- 最も基本的な論理演算は<mark>論理積</mark> (AND) と<mark>論理和</mark> (OR) 及 び否定 (NOT) である。

基本的な 論理演算 (AND, OR, NOT)

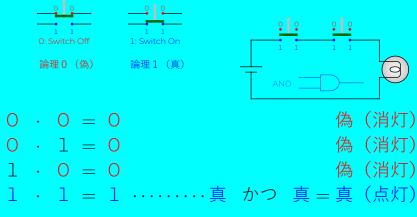

### 基本的な論理演算 1. AND

AND (アンド)

論理積 (かつ) (Verilog HDLの表現)

『例』 F = A · B = A B (F = A & B)

O · O = O 偽

1 · O = O

1 · 1 = 1 ············ 真 かつ 真 = 真

論理積は、入力値がすべて1のときに1を出力する。 それ以外の入力値のときは0を出力する。

$0 \cdot 1 = 0$

偽

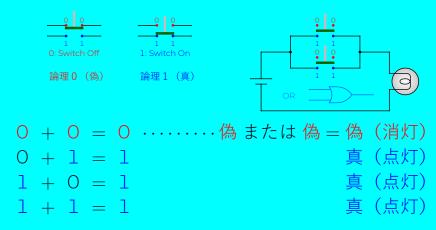

### 基本的な論理演算 2. OR

② OR (オア) 論理和 (または) (Verilog HDLの表現) 『例』 F = A + B (F = A | B)

論理和は、入力値がすべて0のときに0を出力する。 それ以外の入力値のときは1を出力する。

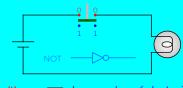

### 基本的な論理演算 3. NOT

NOT (ノット)否定 (Verilog HDLの表現)『例』 F = Ā (F = ~A)

□ = 1 ·············· 偽の否定 = 真 □ = 0 ··········· 真の否定 = 偽

論理否定は、入力された値が0なら1に、 1なら0に反転する。

基本的な 論理ゲート (AND, OR, NOT)

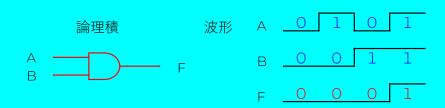

### 基本的な論理ゲート — 1. ANDゲート

論理式  $F = A \cdot B = A B$

#### Verilog HDLの表現:F = A & B

論理積 (AND) は、入力値がすべて 1 のときに 1 を出力する。それ以外の入力値のときは 0 を出力する。

論理積は、入力値がすべて1のときに1を出力する。それ以外の入力値のときは0を出力する。

#### 真理值表

| Α | В | F |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

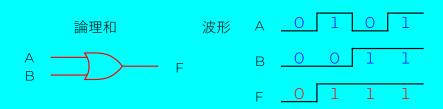

### 基本的な論理ゲート — 2. OR ゲート

#### 論理式 F = A + B

### Verilog HDLの表現:F = A | B

論理和 (OR) は、入力値にいずれか1が入力されたときに1を出力する。それ以外の入力値のときは0を出力する。

論理和は、入力値がすべて0のときに0を出力する。それ以外の入力値のときは1を出力する。

#### 真理値表

| Α | В | F |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

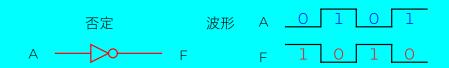

### 基本的な論理ゲート — 3. NOTゲート

#### 論理式 $F = \overline{A}$

### Verilog HDLの表現:F = ~A

否定 (NOT) は、入力された値が1なら0に、0なら1に反転する。

#### 真理值表

| Α | F |

|---|---|

| 0 | 1 |

| 1 | O |

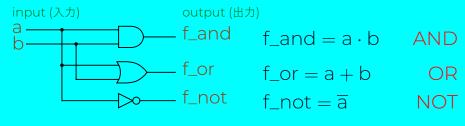

# 論理式と Verilog HDLの書き方

| 集合論  |                | 命題論理 |       | 論理式  |       | Verilog HDL |

|------|----------------|------|-------|------|-------|-------------|

| 積集合  | A∩B            | 連言   | ΑΛΒ   | 論理積  | А·В   | A & B       |

| 和集合  | АИВ            | 選言   | A v B | 論理和  | A + B | A B         |

| 補集合  | A <sup>c</sup> | 否定   | ¬Α    | 否定   | Ā     | ~A          |

| 全体集合 | U              | 真    | Т     | 論理 1 | 1     | 1           |

| 空集合  | Ø              | 偽    | F     | 論理 O | 0     | О           |

他の論理ゲート (XOR、XNOR)

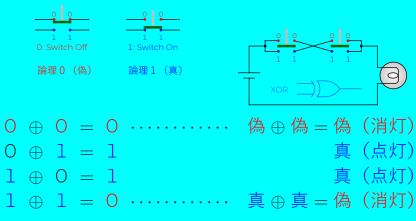

# 排他的論理和 (XOR)

Verilog HDLの表現:F = A ^ B

排他的論理和 XOR (Exclusive Or) A XOR  $B = A \oplus B = \overline{A} \cdot B + A \cdot \overline{B}$

排他的論理和は、二つの入力値が違うとき1を、 それ以外(入力値が同じとき)は、0を出力する。

$$A \oplus A = 0$$

$$A \oplus \overline{A} = 1$$

$$A \oplus 0 = A$$

$$A \oplus 1 = \overline{A}$$

| XOF | ? 真 | 理値表 |

|-----|-----|-----|

| Α   | В   | Ш   |

| 0   | O   | 0   |

| Ο   | 1   | 1   |

| 1   | 0   | 1   |

| 1   | 1   | 0   |

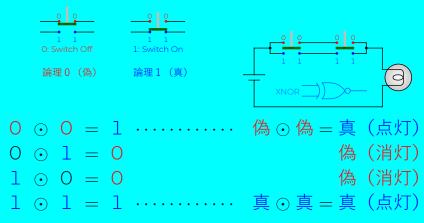

# 否定排他的論理和 (XNOR)

否定排他的論理和 XNOR (Exclusive Not Or)

A XNOR  $B = A \odot B = \overline{A} \cdot \overline{B} + A \cdot B = \overline{A \oplus B}$

Verilog HDLの表現: $F = ^(A ^ B)$

否定排他的論理和は、二つの入力値が同じとき1を、 それ以外(入力値が違うとき)は、0を出力する。

$$A \odot A = 1$$

$$A \odot \overline{A} = 0$$

$$A \odot O = \overline{A}$$

$$A \odot 1 = A$$

#### XNOR 真理值表

| A | В | F |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

# 論理式と Verilog HDLの書き方

|     | 演算    | 論理式                         | Verilog HDL                | ゲート    |

|-----|-------|-----------------------------|----------------------------|--------|

| (1) | AND:  | $F = A \cdot B$             | F = A & B                  | AND    |

| (2) | OR:   | F = A + B                   | $F = A \mid B$             | OR     |

| (3) | NOT:  | $F = \overline{A}$          | F = ~A                     | NOT    |

| (4) | NAND: | $F = \overline{A \cdot B}$  | $F = ^{\sim}(A \& B)$      | NAND — |

| (5) | NOR:  | $F = \overline{A + B}$      | $F = ^{\sim}(A \mid B)$    | NOR    |

| (6) | XOR:  | $F = A \oplus B$            | $F = A \cap B$             | ⇒XOR   |

| (7) | XNOR: | $F = \overline{A \oplus B}$ | $F = ^{\sim}(A ^{\sim} B)$ | XNOR — |

論理演算の理解 雷球を点灯回路

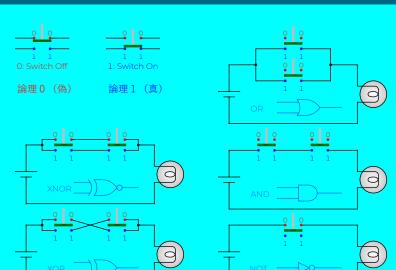

### 論理演算を理解(AND)

論理積は、入力値がすべて1のときに1を、 それ以外の入力値のときは0を出力する。

### 論理演算を理解(OR)

論理和は、入力値がすべて0のときに0を、 それ以外の入力値のときは1を出力する。

## 論理演算を理解(XOR)

排他的論理和は、二つの入力値が違うとき1を、それ以外(入力値が同じとき)は、0を出力する。

### 論理演算を理解(XNOR)

否定排他的論理和は、二つの入力値が同じとき1を、 それ以外(入力値が違うとき)は、0を出力する。

### 論理演算を理解(NOT)

$$\overline{0} = 1 \cdots \overline{1} = 0$$

論理否定は、入力された値が0なら1に、 1なら0に反転する。

### 論理演算を理解(電球を点灯する)

回路の例とその Verilog HDL による実装

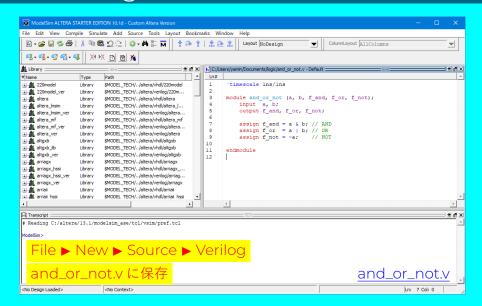

### 回路と Verilog HDLによる実装

```

and_or_not.v

itimescale ins/ins

module and_or_not (a, b, f_and, f_or, f_not);

input a, b;

output f_and, f_or, f_not;

assign f_and = a & b; // AND

assign f_or = a | b; // OR

assign f_not = ~a; // NOT

endmodule

-:--- and_or_not.v All L10 (Verilog)

```

#### and\_or\_not.v

リンク先のファイルをダウンロード

### logic フォルダを作る

Finder  $\rightarrow$   $\mathcal{P}$   $\mathcal{P$

```

yamin@mac ~ % ls -l

yamin@mac ~ % mkdir logic

yamin@mac ~ % cd logic

yamin@mac logic % ls -l

yamin@mac logic % touch and_or_not.v

yamin@mac logic % open -e and_or_not.v

```

Safari ウィンドウで command + a, command + c

Text editor で command + v, command + s, command + w

```

yamin@mac logic % ls -l

yamin@mac logic % cat and_or_not.v

```

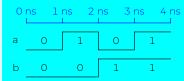

### テストベンチ — シミュレーションのため

```

and or not tb.v

`timescale 1ns/1ns

module and or not tb;

req a, b;

wire f_and, f_or, f_not;

and_or_not i0 (a, b, f_and, f_or, f_not);

initial begin

#0 a = 0;

#0 b = 0:

#4 $finish;

end

always #1 a = \sim a:

always #2 b = \sim b:

initial begin

$dumpfile ("and_or_not.vcd");

$dumpvars:

end

endmodule

-:--- and or not tb.v All L22

(Verilog)

Beginning of buffer

```

#### 入力信号の値を指定する

and\_or\_not\_tb.v

リンク先のファイルをダウンロード

### テストベンチを作る

```

logic のターミナルで

```

```

yamin@mac logic % touch and_or_not_tb.v

yamin@mac logic % open -e and_or_not_tb.v

```

Safari ウィンドウで command + a, command + c

Text editor で command + v, command + s, command + w

```

yamin@mac logic % ls -l

yamin@mac logic % cat and_or_not_tb.v

```

emacs がお勧めである

yamin@mac logic % emacs and\_or\_not\_tb.v &

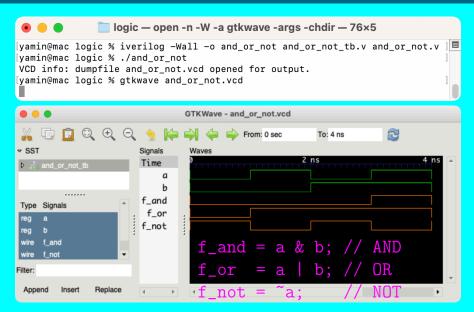

### シミュレーションと波形

iverilog Ł gtkwave o インストール

### Homebrewのインストール

iverilog と gtkwave をインストールするには、まず Homebrew をインストールする必要がある。

Homebrew をインストールするには、次の Web ページを参照してください。

M1 MacBook Air Package Installation

そのあと、brew コマンドを使用してパッケージをイ ンストールできる。

#### iverilog と gtkwave のインストール

#### iverilog をインストールする:

% brew install icarus-verilog

% iverilog -Wall -o and\_or\_not and\_or\_not\_tb.v and\_or\_not.v

% vvp and\_or\_not

VCD info: dumpfile and\_or\_not.vcd opened for output.

#### gtkwave をインストールする:

% brew install --HEAD randomplum/gtkwave/gtkwave

% gtkwave and\_or\_not.vcd &

論理式と回路の例

## 論理式と論理回路の例 (真理値表)

論理式の例:  $Y = \overline{S} \cdot AO + S \cdot A1$

その論理式の真理値表

|   | 入力 |    |   |      |      | 出力 |

|---|----|----|---|------|------|----|

| S | Al | ΑO | S | Ī∙A0 | S·Al | Y  |

| 0 | O  | 0  | 1 | 0    | 0    | 0  |

| O | O  | 1  | 1 | 1    | 0    | 1  |

| O | 1  | O  | 1 | 0    | 0    | 0  |

| 0 | 1  | 1  | 1 | 1    | O    | 1  |

| 1 | 0  | 0  | 0 | 0    | 0    | 0  |

| 1 | O  | 1  | 0 | 0    | 0    | 0  |

| 1 | 1  | O  | 0 | 0    | 1    | 1  |

| 1 | 1  | 1  | 0 | O    | 1    | 1  |

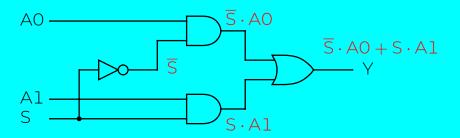

# 論理式と論理回路の例 (回路図)

論理式の例:  $Y = \overline{S} \cdot AO + S \cdot A1$

その論理式の論理回路

優先順位: (高い) 否定 → 論理積 → 論理和 (低い)

#### 論理式と論理回路の例 (Verilog HDL)

論理式の例:  $Y = \overline{S} \cdot AO + S \cdot A1$

その論理式の Verilog HDL による回路

```

'timescale 1ns/1ns

module example (A0, A1, S, Y);

input A0, A1, S;

output Y;

assign Y = ~S & A0 | S & A1;

endmodule

```

優先順位: (高い) 否定 → 論理積 → 論理和 (低い)

#### 論理式と論理回路の例 (Verilog HDL)

論理式の例:  $Y = \overline{S} \cdot AO + S \cdot A1$

その論理式の Verilog HDL による回路

```

example.v

'timescale 1ns/1ns

module example (A0, A1, S, Y);

input A0, A1, S;

output Y;

assign Y = ~S & A0 | S & A1;

endmodule

-:--- example.v All L8 (Veril

```

example.v

論理式:

$$Y = \overline{S} \cdot AO + S \cdot A1$$

$\downarrow \downarrow \qquad \downarrow \qquad \downarrow$

Verilog HDL:  $Y = \overline{S} \& AO + S \cdot A1$

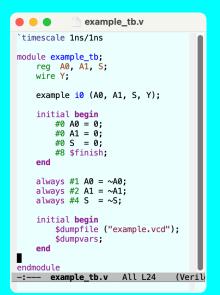

#### 論理式と論理回路の例 (テストベンチ)

#### 入力信号の値を指定する

```

Ons 2 ns 4 ns 6 ns 8 ns

AO 0 1 0 1 0 1 0 1

A1 0 0 1 1 0 0 1 1

S 0 0 0 0 1 1 1 1

```

example\_tb.v

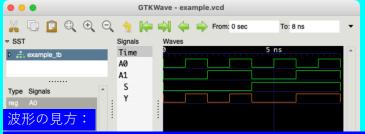

# 論理式と論理回路の例 (波形)

```

logic — open -n -W -a gtkwave -args -chdir — 76×5

yamin@mac logic % iverilog -Wall -o example example_tb.v example.v

yamin@mac logic % ./example

VCD info: dumpfile example.vcd opened for output.

yamin@mac logic % gtkwave example.vcd

```

S = 0 の時、 $Y = \overline{S} \cdot AO + S \cdot A1 = 1 \cdot AO + O \cdot A1 = AO + O = AO$

S=1 の時、 $Y=\overline{S}\cdot AO+S\cdot A1=O\cdot AO+1\cdot A1=O+A1=A1$

#### 論理演算と論理ゲート

#### まとめ

- 0と1の表現(電圧の高/低)

- 論理演算と論理ゲート

- ▶ 基本的な論理演算と論理ゲート: AND、OR、NOT

- ▶ ほかのゲート: NAND、NOR、XOR、XNOR

- 論理演算の理解(電球を点灯する回路)

- 真理値表、論理式と論理回路

- ハードウェア記述言語

- Verilog HDL (Hardware Description Language)

- シミュレーションのためのテストベンチ (Test bench)

- iverilog と gtkwave

# 課題

#### 課題 | (100 点)

問題 1:排他的論理和  $XOR:A \oplus B = \overline{A} \cdot B + A \cdot \overline{B}$

問題:A⊕B⊕Cの真理値表を完成して下さい。

注意: $A \oplus B \oplus C = (A \oplus B) \oplus C$

| 入力 |   |   |   |   | 出力  |                        |              |                       |

|----|---|---|---|---|-----|------------------------|--------------|-----------------------|

| Α  | В | С | Ā | B | Ā·B | $A \cdot \overline{B}$ | $A \oplus B$ | $A \oplus B \oplus C$ |

| 0  | 0 | 0 | 1 | 1 |     |                        |              |                       |

| 0  |   |   |   |   |     |                        |              |                       |

| 0  |   |   |   |   |     |                        |              |                       |

| 0  |   |   |   |   |     |                        |              |                       |

| 1  |   |   |   |   |     |                        |              |                       |

| 1  |   |   |   |   |     |                        |              |                       |

| 1  |   |   |   |   |     |                        |              |                       |

| 1  | 1 | 1 | 0 | 0 |     |                        |              |                       |

# 課題 | (100 点)

iverilog -Wall -o xor3 xor3\_tb.v xor3.v

vvp xor3

gtkwave xor3.vcd &

レポート pdf: logic-01-24k0000-法政花子.pdf レポート tex: logic-01-24k0000-法政花子.tex

TeX のインストール: Mac Package Installation

#### 課題 | (100 点)

If you cannot install gtkwave, please use the testbench <u>xor3\_testbench.v</u>. Then the inputs and output can be shown as follows.

```

iverilog -Wall -o xor3 xor3_testbench.v xor3.v

vvp xor3

VCD info: dumpfile xor3.vcd opened for output.

time

0 ns: 0 0 0 0

1 ns: 0 0 1 1

2 ns: 0 1 0 1

3 ns: 0 1 1 0

4 ns: 1 0 0 1

5 ns: 1 0 1 0

6 ns: 1 1 0 0

7 ns: 1 1 1 1

8 ns:

```

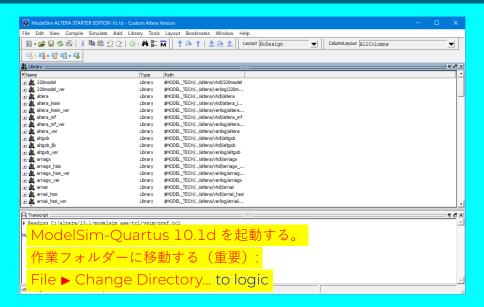

# Windows PC

でのやり方

#### 1. 作業フォルダーを作成する

まず最初に、作業フォルダーを作成する。例えば

C:\Users\your\_account\Documents\logic

これからのすべてのデザインはこの作業フォルダーで 行われなければならない。

logic

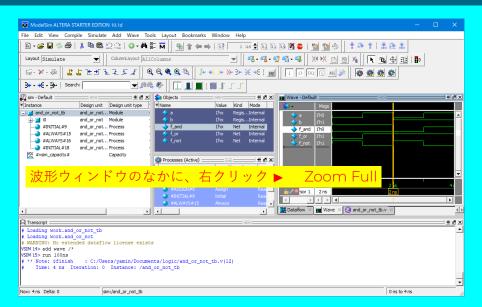

#### 2. ModelSim を起動

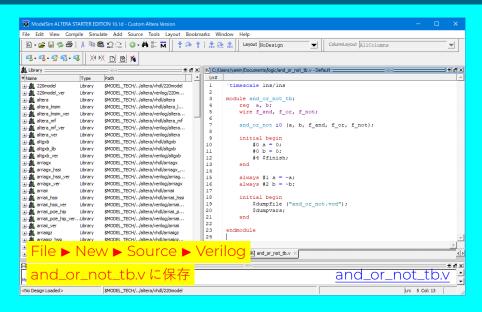

#### 3. Verilog HDLファイルを入力

#### 4. テストベンチを入力

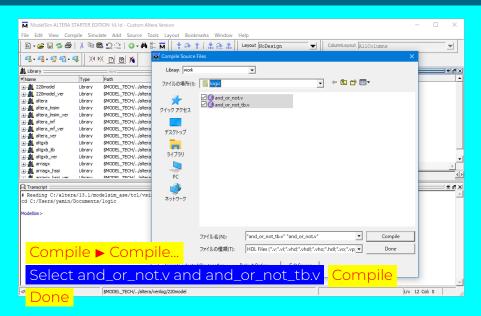

#### 5. 論理合成

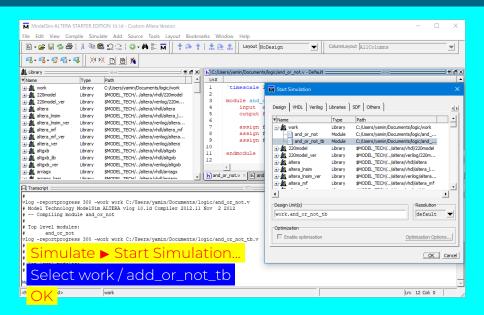

#### 6. シミュレーション

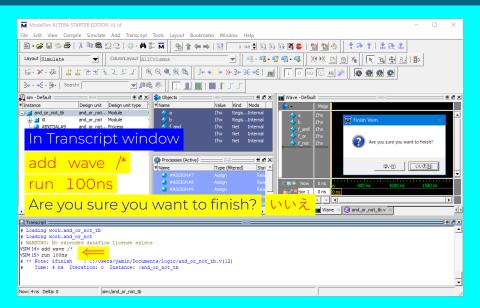

#### 7. コマンドを実行

#### 8. 波形を確認