# 論理回路入門(13)

同期式N進カウンターの設計

李 亜民

2022年12月20日(火)

## 同期式N進カウンターの設計

#### ポイント

- 同期式 N 進カウンター

- ▶ DFF で同期式 N 進カウンター

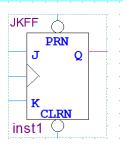

- ▶ JKFF で同期式N進カウンター

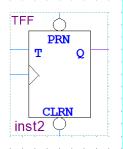

- ▶ TFF で同期式 N 進カウンター

- 非同期式カウンター

- 非同期式 FIFO

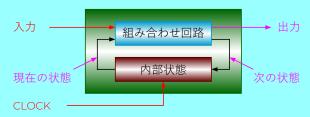

# 順序回路

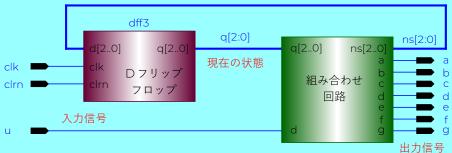

- 順序回路は内部状態と入力信号で出力が決まる回路である。

- 順序回路の構成:

- 記憶素子 (D フリップフロップなど)

- ★ 現在の状態を記憶しておくため

- ② 組み合わせ回路

- ★ 状態遷移関数 (次の状態)

- ★ 出力関数

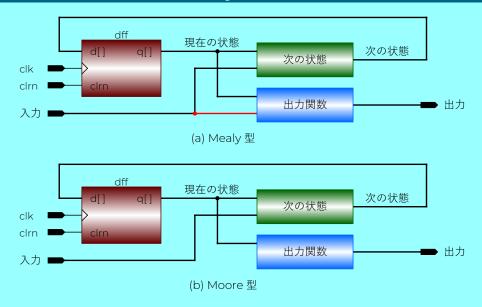

# 順序回路 — Mealy 型と Moore 型

# 順序回路設計の手順

- 📵 問題を理解する。

- ② 状態遷移図をつくる。

- ⑤ FF の数を決める  $(n = \lceil \log_2 N \rceil, N$  は状態の数)。

- 個 各状態に n ビットの番号を付け、真理値表をつくる。

- ▶ 次の状態の真理値表をつくる。

- ▶ 出力関数の真理値表をつくる。

- ⑤ 真理値表から論理式をつくる (どの条件で出力が 1 になるか)。

- ▶ カルノー図を用いて論理式を簡単化する。

- 論理式から回路をつくる。

- アストベンチをつくる (シミュレーションするため)。

- 📵 回路をシミュレーションする (回路設計の正当性検証)。

- 与えられた回路の動作を理解する(波形の説明)。

### 同期式N進カウンターの設計

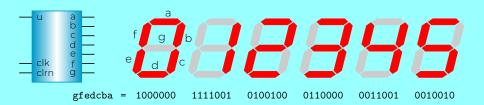

問題: 7セグメント LED を使いカウントアップ / カウントダウンする回路を作成しよう。

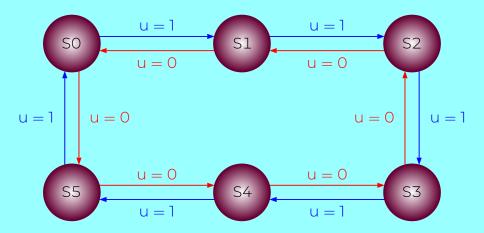

- カウント範囲: 0~5

- $u = 0 ( ) ) : 0, 5, 4, 3, 2, 1, 0, 5, 4, 3, \cdots$

- 7セグメント LED で表示する (O: 点灯; 1: 消灯)

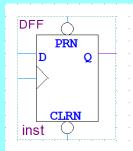

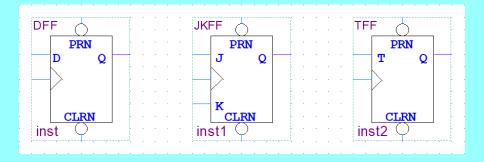

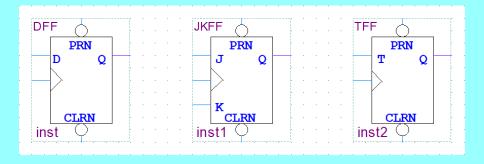

#### フリップフロップ

DFF: CLK の立ち上がりで、 $Q_{next} = D$

JKFF: CLK の立ち上がりで、 $Q_{next} = J \overline{Q} + \overline{K} Q$

TFF: CLK の立ち上がりで、 $Q_{next} = T \overline{Q} + \overline{T} Q$

#### 0~5カウンター:

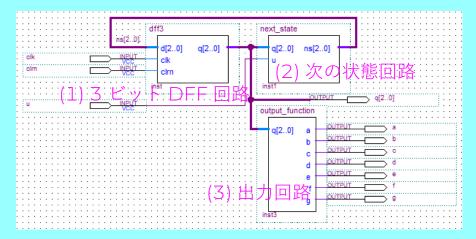

- 状態数: 6 (0, 1, 2, 3, 4, 5)

- 3 ビット DFF を使う ([Log<sub>2</sub>6] = 3)

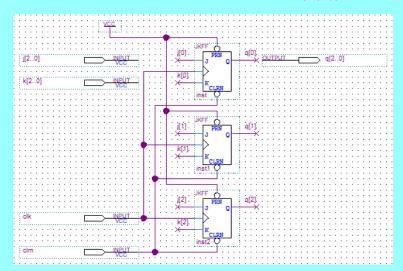

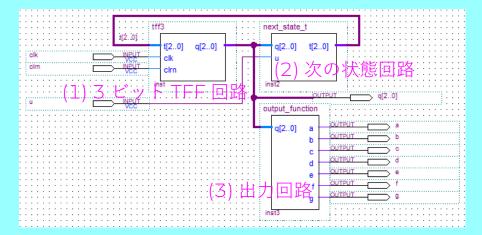

- カウント全体の回路:

#### 次の状態

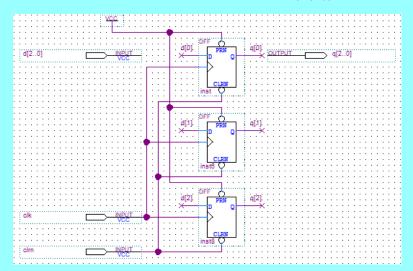

#### 0~5 カウンター: 3 ビット DFF 回路:

#### 0~5カウンター: 状態遷移図:

#### 0~5カウンター: 状態遷移表:

|       | 現在の  | り状態  |      | 入力 | 次の状態       |       |       |       |

|-------|------|------|------|----|------------|-------|-------|-------|

|       | q[2] | q[1] | q[0] | u  |            | ns[2] | ns[1] | ns[0] |

| SO    | 0    | О    | 0    | 1  | Sl         | 0     | 0     | 1     |

|       |      |      |      | 0  | S5         | 1     | 0     | 1     |

| Sl    | 0    | 0    | 1    | 1  | S2         | 0     | 1     | 0     |

|       |      |      |      | 0  | S0         | 0     | 0     | 0     |

| S2    | 0    | 1    | 0    | 1  | S3         | 0     | 1     | 1     |

|       |      |      |      | 0  | Sl         | 0     | 0     | 1     |

| S3    | 0    | 1    | 1    | 1  | S4         | 1     | 0     | 0     |

|       |      |      |      | 0  | S2         | 0     | 1     | 0     |

| S4    | 1    | 0    | 0    | 1  | S5         | 1     | 0     | 1     |

|       |      |      |      | 0  | S3         | 0     | 1     | 1     |

| S5    | 1    | 0    | 1    | 1  | SO         | 0     | 0     | 0     |

|       |      |      |      | 0  | S4         | 1     | 0     | 0     |

| 入力として | 1    | 1    | 0    | X  | Don't care | X     | Х     | X     |

| 存在しない | 1    | 1    | 1    | Х  | ドントケア      | Х     | Х     | X     |

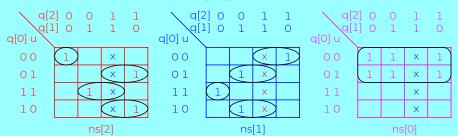

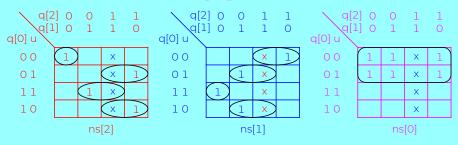

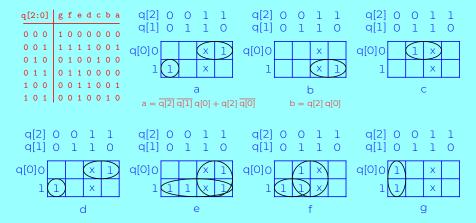

#### 0~5カウンター: 次の状態:

#### 0~5カウンター: 次の状態:

$ns[2] = \overline{q[2]} \ \overline{q[1]} \ \overline{q[0]} \ \overline{u} + q[1] \ q[0] \ u + q[2] \ \overline{q[0]} \ u + q[2] \ q[0] \ \overline{u}$

#### 0~5カウンター: 次の状態:

#### 0~5カウンター: 次の状態:

$$\begin{split} \text{ns}[2] &= \overline{q[2]} \; \overline{q[1]} \; \overline{q[0]} \; \overline{u} + q[1] \; q[0] \; u + q[2] \; \overline{q[0]} \; u + q[2] \; q[0] \; \overline{u} \\ \text{ns}[1] &= \overline{q[2]} \; \overline{q[1]} \; q[0] \; u + q[1] \; \overline{q[0]} \; u + q[1] \; q[0] \; \overline{u} + q[2] \; \overline{q[0]} \; \overline{u} \\ \text{ns}[0] &= \overline{q[0]} \end{split}$$

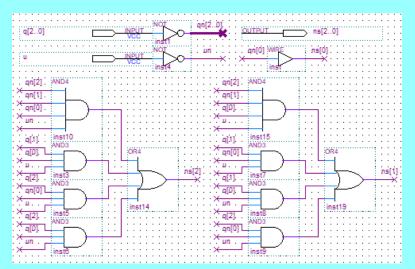

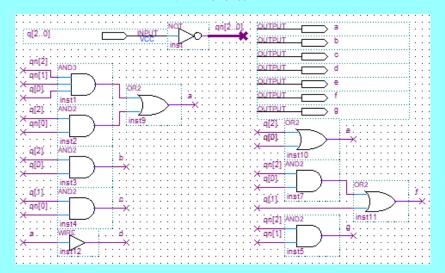

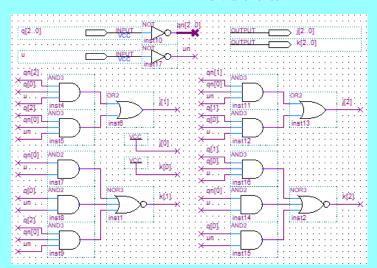

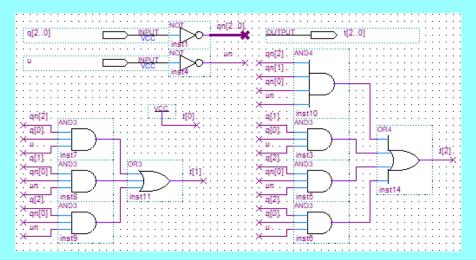

#### 0~5 カウンター: 次の状態回路:

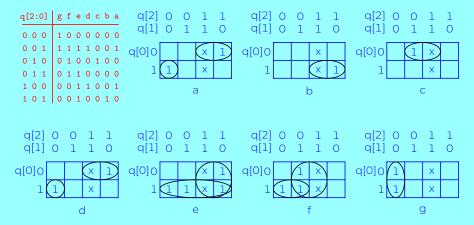

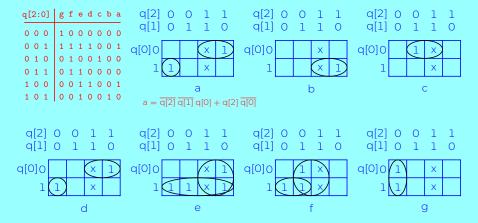

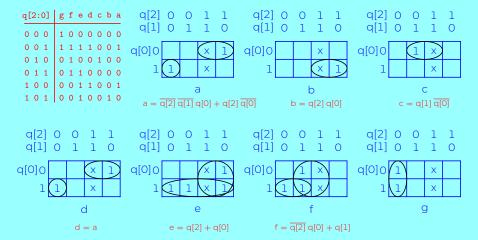

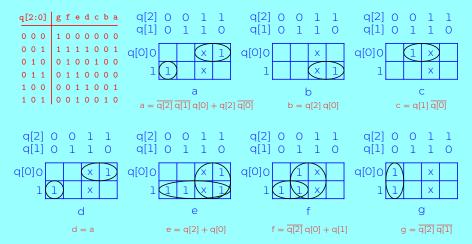

O~5 カウンター: 出力 (O: 点灯; 1: 消灯):

#### ○ ~ 5 カウンター: 出力 (O: 点灯; 1: 消灯):

#### ○ ~ 5 カウンター: 出力 (O: 点灯; 1: 消灯):

#### O~5 カウンター: 出力 (O: 点灯; 1: 消灯):

#### O ~ 5 カウンター: 出力 (O: 点灯; 1: 消灯):

#### O ~ 5 カウンター: 出力 (O: 点灯; 1: 消灯):

#### O~5 カウンター: 出力 (O: 点灯; 1: 消灯):

#### O~5 カウンター: 出力 (O: 点灯; 1: 消灯):

#### 0~5カウンター: 出力回路:

#### 0~5 カウンター: 全体の回路:

```

'timescale 1ns/1ps // unit = 1 ns; accuracy = 1 ps

module counter6_tb;

reg u,clk,clrn;

wire a,b,c,d,e,f,g;

wire [2:0] q;

counter6 i1 (

.u(u),

.clk(clk),

.clrn(clrn).

.a(a),.b(b),.c(c),.d(d),.e(e),.f(f),.g(g),

.q(q)

initial begin

#0 clk = 1; clrn = 0; u = 1;

#1 clrn = 1;

#18 u = 0:

#25 $stop;

end

always #1 clk = ~clk;

endmodul e

```

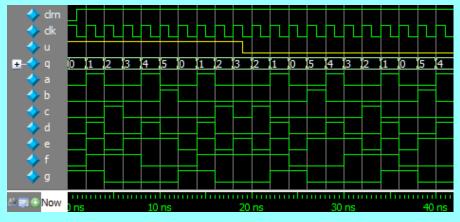

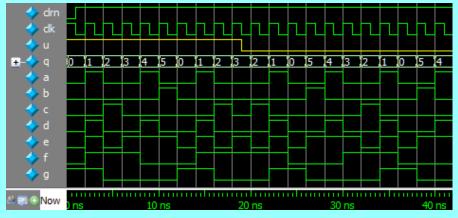

#### ○~5 カウンター: シミュレーション波形:

counter6\_tb.v Count Up

Count Down

# J K F F で 同 期 式 N 進 カ ウ ン タ ー の 設 計

### フリップフロップ

DFF: CLK の立ち上がりで、 $Q_{next} = D$

JKFF: CLK の立ち上がりで、 $Q_{next} = J \overline{Q} + \overline{K} Q$

TFF: CLK の立ち上がりで、 $Q_{next} = T \overline{Q} + \overline{T} Q$

• JKFF: CLK の立ち上がりで、 $Q_{next} = J \overline{Q} + \overline{K} Q \cdot \cdot \cdot \cdot \cdot \cdot (= ns)$

例:

$$ns = A \overline{q} + B q + C$$

$= A \overline{q} + B q + C (\overline{q} + q)$

$= A \overline{q} + B q + C \overline{q} + C q$

$= (A + C) \overline{q} + (B + C) q$

$= j \overline{q} + \overline{k} q$

- j = A + C

- $k = \overline{B + C}$

• JKFF: CLK の立ち上がりで、 $Q_{next} = J \overline{Q} + \overline{K} Q \cdots (= ns)$

• JKFF: CLK の立ち上がりで、

$$Q_{next} = J \overline{Q} + \overline{K} Q \cdot \cdot \cdot \cdot \cdot \cdot (= ns)$$

•

$$ns[0] = \overline{q[0]} = 1 \cdot \overline{q[0]} + 0 \cdot q[0] = j[0] \cdot \overline{q[0]} + \overline{k[0]} \cdot q[0]$$

• JKFF: CLK の立ち上がりで、

$$Q_{next} = J \overline{Q} + \overline{K} Q \cdot \cdot \cdot \cdot \cdot \cdot (= ns)$$

•

$$ns[0] = \overline{q[0]} = 1 \cdot \overline{q[0]} + 0 \cdot q[0] = j[0] \cdot \overline{q[0]} + \overline{k[0]} \cdot q[0]$$

$$ightharpoonup k[0] = \overline{0} = 1 \cdot \cdots \cdot \overline{k[0]} q[0]$$

•

$$ns[1] = \overline{q[2]} \, \overline{q[1]} \, q[0] \, u + q[1] \, \overline{q[0]} \, u + q[1] \, q[0] \, \overline{u} + q[2] \, \overline{q[0]} \, \overline{u}$$

$$j[1] = \overline{q[2]} q[0] u + q[2] \overline{q[0]} \overline{u} \cdots j[1] \overline{q[1]}$$

$$\qquad \qquad \mathsf{k}[1] = \overline{\mathsf{q}[0]} \; \mathsf{u} + \mathsf{q}[0] \; \overline{\mathsf{u}} + \mathsf{q}[2] \; \overline{\mathsf{q}[0]} \; \overline{\mathsf{u}} \; \cdots \cdots \cdots \overline{\mathsf{k}[1]} \; \mathsf{q}[1]$$

• JKFF: CLK の立ち上がりで、

$$Q_{next} = J \overline{Q} + \overline{K} Q \cdots (= ns)$$

•

$$ns[0] = \overline{q[0]} = 1 \cdot \overline{q[0]} + 0 \cdot q[0] = j[0] \cdot \overline{q[0]} + \overline{k[0]} \cdot q[0]$$

$$ightharpoonup k[0] = \overline{0} = 1 \cdot \cdots \cdot \overline{k[0]} q[0]$$

•

$$ns[1] = \overline{q[2]} \, \overline{q[1]} \, q[0] \, u + q[1] \, \overline{q[0]} \, u + q[1] \, q[0] \, \overline{u} + q[2] \, \overline{q[0]} \, \overline{u}$$

$$k[1] = \overline{q[0]} u + q[0] \overline{u} + q[2] \overline{q[0]} \overline{u} \cdot \cdots \cdot \overline{k[1]} q[1]$$

•

$$ns[2] = \overline{q[2]} \, \overline{q[1]} \, \overline{q[0]} \, \overline{u} + q[1] \, q[0] \, u + q[2] \, \overline{q[0]} \, u + q[2] \, q[0] \, \overline{u}$$

▶

$$k[2] = q[1] q[0] u + \overline{q[0]} u + q[0] \overline{u} \cdot \cdots \cdot \overline{k[2]} q[2]$$

# JKFF で同期式 N 進力ウンターの設計

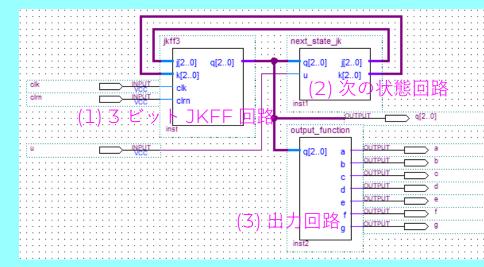

#### ○ ~ 5 カウンター: 3 ビット JKFF 回路:

# JKFF で同期式N進カウンターの設計

#### 0~5 カウンター: 次の状態回路:

# JKFF で同期式 N 進力ウンターの設計

#### 0~5 カウンター: 全体の回路:

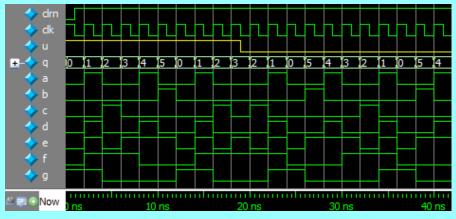

# JKFF で同期式N進カウンターの設計

#### 0~5 カウンター: シミュレーション波形:

counter6\_jk\_tb.v Count Up

Count Down

### フリップフロップ

DFF: CLK の立ち上がりで、 $Q_{next} = D$

JKFF: CLK の立ち上がりで、 $Q_{next} = J \overline{Q} + \overline{K} Q$

TFF: CLK の立ち上がりで、 $Q_{next} = T \overline{Q} + \overline{T} Q$

#### ○ ~ 5 カウンター: 状態遷移表 (t = 1: Toggle)

|      | 現在の状態 |      |      |   | 次の状態      |       |       |       |      |      |      |

|------|-------|------|------|---|-----------|-------|-------|-------|------|------|------|

|      | q[2]  | q[1] | q[0] | u |           | ns[2] | ns[1] | ns[0] | t[2] | t[1] | t[0] |

| SO   | 0     | 0    | 0    | 1 | Sl        | 0     | 0     | 1     | 0    | 0    | 1    |

|      |       |      |      | 0 | S5        | 1     | 0     | 1     | 1    | 0    | 1    |

| Sl   | 0     | 0    | 1    | 1 | S2        | 0     | 1     | 0     | 0    | 1    | 1    |

|      |       |      |      | 0 | S0        | 0     | 0     | 0     | 0    | 0    | 1    |

| S2   | 0     | 1    | 0    | 1 | S3        | 0     | 1     | 1     | 0    | 0    | 1    |

|      |       |      |      | 0 | Sl        | 0     | 0     | 1     | 0    | 1    | 1    |

| S3   | 0     | 1    | 1    | 1 | S4        | 1     | 0     | 0     | 1    | 1    | 1    |

|      |       |      |      | 0 | S2        | 0     | 1     | 0     | 0    | 0    | 1    |

| S4   | 1     | 0    | 0    | 1 | S5        | 1     | 0     | 1     | 0    | 0    | 1    |

|      |       |      |      | 0 | S3        | 0     | 1     | 1     | 1    | 1    | 1    |

| S5   | 1     | 0    | 1    | 1 | SO        | 0     | 0     | 0     | 1    | 0    | 1    |

|      |       |      |      | 0 | S4        | 1     | 0     | 0     | 0    | 0    | 1    |

| 入力と  | ιτ 1  | 1    | 0    | × | Don't car | re X  | X     | X     | Х    | Χ    | Х    |

| 存在した | ない 1  | 1    | 1    | X | ドントケ:     | r X   | Х     | Х     | Х    | Χ    | X    |

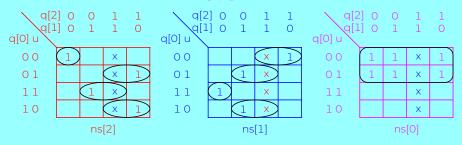

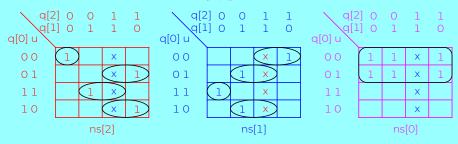

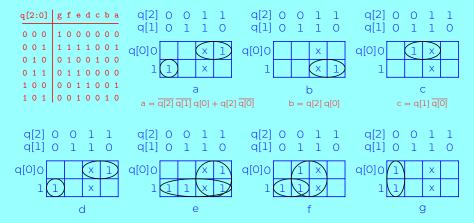

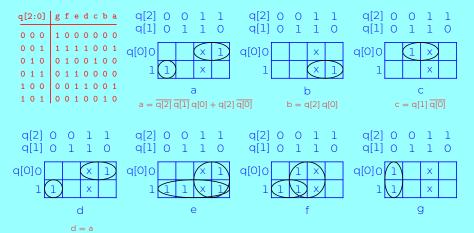

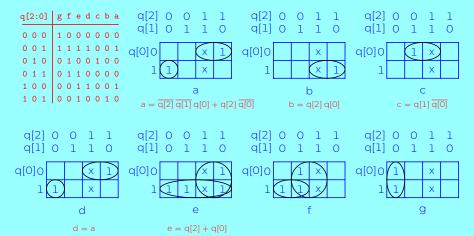

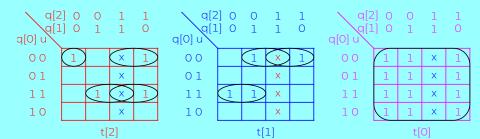

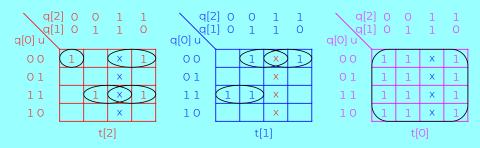

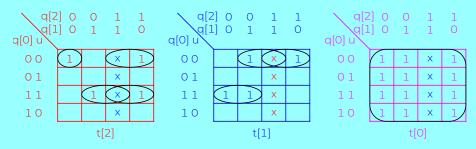

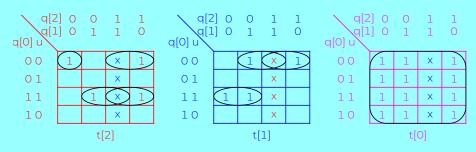

#### 0~5カウンター: 次の状態:

#### 0~5 カウンター: 次の状態:

$$t[2] = q[1]\,q[0]\,u + q[2]\,\overline{q[0]}\,\overline{u} + q[2]\,q[0]\,u + \overline{q[2]}\,\overline{q[1]}\,\overline{q[0]}\,\overline{u}$$

#### 0~5カウンター: 次の状態:

$$t[2] = q[1] q[0] u + q[2] \overline{q[0]} \overline{u} + q[2] q[0] u + \overline{q[2]} \overline{q[1]} \overline{q[0]} \overline{u}$$

$$t[1] = \overline{q[2]} q[0] u + q[1] \overline{q[0]} \overline{u} + q[2] \overline{q[0]} \overline{u}$$

#### 0~5カウンター: 次の状態:

$$t[2] = q[1] q[0] u + q[2] \overline{q[0]} \overline{u} + q[2] q[0] u + \overline{q[2]} \overline{q[1]} \overline{q[0]} \overline{u}$$

$$t[1] = \overline{q[2]} q[0] u + q[1] \overline{q[0]} \overline{u} + q[2] \overline{q[0]} \overline{u}$$

$$t[0] = 1$$

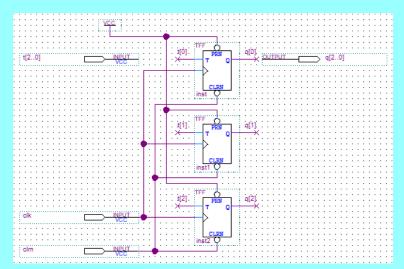

#### ○ ~ 5 カウンター: 3 ビット TFF 回路:

#### 0~5 カウンター: 次の状態回路:

#### 0~5 カウンター: 全体の回路:

#### 0~5 カウンター: シミュレーション波形:

counter6\_t\_tb.v Count Up

Count Down

# デジタル時計の実装

#### FPGA で実装したデジタル時計

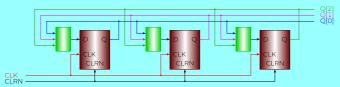

### 同期式と非同期式カウンター

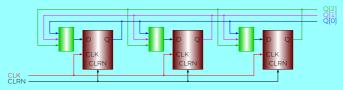

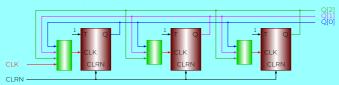

● 同期式 (Synchronous) とは、構成するフリップフロップの動作が同一のクロックで行われる方式のことである。

### 同期式と非同期式カウンター

● 同期式 (Synchronous) とは、構成するフリップフロップの動作が同一のクロックで行われる方式のことである。

● 非同期式 (Asynchronous) とは、カウンターへの入力と各フリップフロップの出力の変化により、自身のフリップフロップの入力が決定され、その変化で動作する方式のことである。

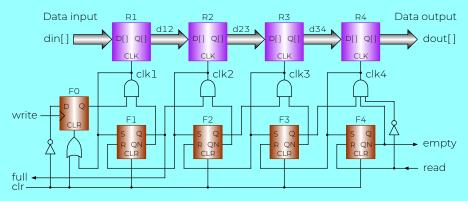

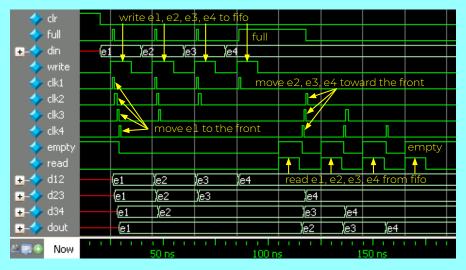

# 非同期式FIFOの設計

FIFO: First-In-First-Out (Queue — # 1 – )

R1、R2、R3、R4:FIFO レジスター (深さ:4) clk1、clk2、clk3、clk4:非同期 clock

# 非同期式FIFOの設計

write: write data to FIFO; read: read data from FIFO.

# 同期式N進カウンターの設計

#### まとめ

- 同期式 N 進カウンター

- ▶ DFF で同期式 N 進カウンター

- ▶ JKFF で同期式N進カウンター

- ▶ TFF で同期式 N 進カウンター

- 非同期式カウンター

- 非同期式 FIFO

# 課題 XIII (100 点 + 100 点)

7セグメント LED を使い同期式 <math>10 進カウントアップ / カウントダウンする回路を、 DFF を用いて設計し、動作検証シミュレーションして下さい (Don't Care 項を利用)。

注意:AND5、OR5 を使用せず、

AND6、OR6 を使用してください。

第6回資料 P20 を参照してください。

- カウント範囲: 0~9

- 7セグメント LED で表示する (O: 点灯; 1: 消灯)

# オプション (+50 点)

7セグメント LED を使い同期式 10 進カウントアップ / カウントダウンする回路を、JKFF を用いて設計し、動作検証シミュレーションして下さい (Don't Care 項を利用)。

- カウント範囲: 0~9

- 7セグメント LED で表示する (O: 点灯; 1: 消灯)

# オプション (+50 点)

7セグメント LED を使い同期式 <math>10 進カウントアップ / カウントダウンする回路を、 TFF を用いて設計し、動作検証シミュレーションして下さい (Don't Care 項を利用)。

- カウント範囲: 0~9

- 7セグメント LED で表示する (O: 点灯; 1: 消灯)

#### Verilog HDL による課題の実装

#### [1]. 4 ビット DFF の設計

#### Verilog HDL による課題の実装

#### [2]. 次の状態回路の設計

上記コードを完成しシミュレーションして下さい。

#### Verilog HDL による課題の実装

#### [3]. 出力関数の回路の設計

```

module cnt10output (q, seven_seg);

input [3:0] q; // current state

output [6:0] seven_seg; // output: 7-seg LED control

assign seven_seg[0] =

: // a

assign seven_seg[1] =

: // b

assign seven_seg[2] =

; // c

assign seven_seg[3] =

; // d

assign seven_seg[4] =

; // e

assign seven_seg[5] =

: // f

assign seven_seg[6] =

; // g

endmodul e

```

上記コードを完成しシミュレーションして下さい。

#### Verilog HDL による課題の実装

[全体]. 10 進カウントアップ/カウントダウンする回路の設計

```

module cnt10top (clk, clrn, u, a, b, c, d, e, f, g);

input clk, clrn, u;

// inputs

output a, b, c, d, e, f, g;

// 7-seg outputs

wire [6:0] seven_seg;

// internal wire

wire [3:0] p;

// next state

wire [3:0] q;

// current state

cnt10dff4 i1 (

); // [1]. 4-bit D flip flops

cnt10nextstate i2 (

); // [2]. next state

); // [3]. output function

cnt10output i3 (

assign {g, f, e, d, c, b, a} = seven_seg; // 7-seg outputs

endmodule.

```

上記コードを完成しシミュレーションして下さい。