### 論理回路入門(11) ラッチとフリップフロップ

李 亜民

2022年12月6日(火)

### ラッチとフリップフロップ

#### ポイント

- 順序回路

- RS ラッチ (RS Latch)

- D ラッチ (D Latch)

- D フリップフロップ (DFF, DFFE)

- Tフリップフロップ (TFF)

- JK フリップフロップ (JKFF)

- レジスタ (Register)

- レジスタファイル (Register File)

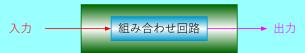

### 論理回路の種類

組み合わせ回路 (Combinational Circuit): 現在の入力 のみで出力が決まる回路である。

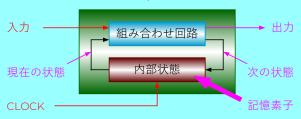

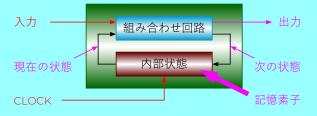

順序回路 (Sequential Circuit): 内部状態と入力信号で 出力が決まる回路である。有限状態機械 (Finite state machine — FSM) とも呼ばれる。

### 順序回路

● 順序回路 (Sequential Circuit): 内部状態と入力信号で 出力が決まる回路である。有限状態機械 (Finite state machine — FSM) とも呼ばれる。

● 順序回路の例:自動販売機の制御回路

どれだけのお金が入れられたかを記憶しなければならない。

### 記憶素子の種類

- ラッチ (Latch)

- ▶ RS ラッチ (RS Latch)

- ▶ Dラッチ (D Latch)

- フリップフロップ (Flip Flop)

- ▶ D フリップフロップ (DFF, DFFE)

- ▶ Tフリップフロップ (TFF)

- ▶ JKフリップフロップ (JKFF)

- メモリ (Memory)

- SRAM (Static Rondom Access Memory)

- DRAM (Dynamic Rondom Access Memory)

- ROM (Read Only Memory)

- ▶ CAM (Content Addressable Memory) 連想メモリ

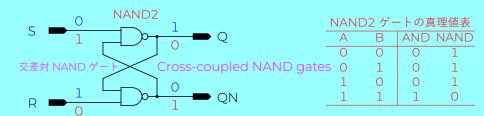

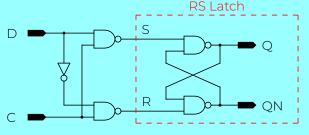

#### RS ラッチ

S: Set, active low (0 の時、セットする (Q = 1))

R: Reset, active low (0 の時、リセットする (Q = 0))

•

$$S = 1$$

,  $R = 0$ : Reset  $(Q = 0)$ ·····リセット

#### Dラッチ

| NANE | )2 ゲー | - 卜の真理値表 |

|------|-------|----------|

| Λ    |       |          |

| 147 (142 | 17 (1102 ) |     | 1 9 美工匠区 |  |  |

|----------|------------|-----|----------|--|--|

| Α        | В          | AND | NAND     |  |  |

| 0        | 0          | 0   | 1        |  |  |

| Ο        | 1          | 0   | 1        |  |  |

| 1        | Ο          | 0   | 1        |  |  |

| 1        | 1          | 1   | Ο        |  |  |

|          |            |     |          |  |  |

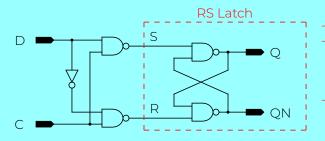

$$\bullet$$

C = 1, D = 0: S = 1, R = 0, Q = 0 = D

$$\bullet$$

C = 1, D = 1: S = 0, R = 1, Q = 1 = D

•

$$C = 0$$

,  $D = x$ :  $S = 1$ ,  $R = 1$ , No change  $S = 0$ ,  $R = 0$  の場合はない

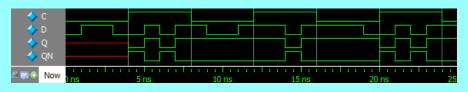

#### D ラッチシミュレーション

| NAND2 ゲートの真理値表 |   |     |      |  |  |  |

|----------------|---|-----|------|--|--|--|

| Α              | В | AND | NANE |  |  |  |

| 0              | 0 | 0   | 1    |  |  |  |

| Ο              | 1 | 0   | 1    |  |  |  |

| 1              | Ο | Ο   | 1    |  |  |  |

| 1              | 1 | 1   | Ο    |  |  |  |

d\_latch\_tb.v

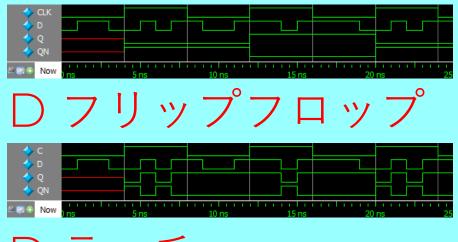

入力 C=1 の時、出力 Q=D(データ入力はデータ出力で伝わる) 入力 C=0 の時、出力 Q は変化なし(以前のデータ出力を保持する)

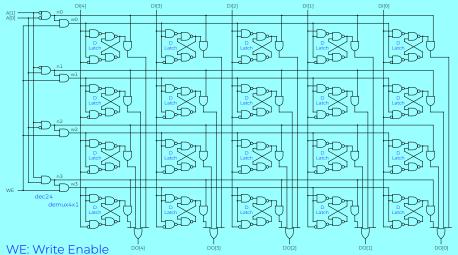

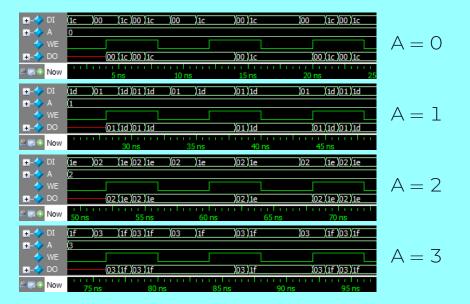

## D ラッチでSRAMの実装 (回路)

4 words: 2-bit address A[1..0]:  $2^2 = 4$

5 bits/word: data-in DI[4..0]; data-out DO[4..0]

## D ラッチでSRAMの実装 (波形)

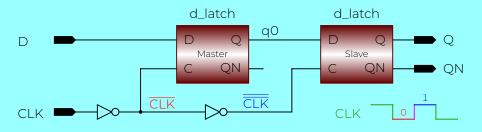

## Dフリ゙ップフロップ (DFF)

CLK = 0 の時、 $\overline{CLK} = 1$ 、Master q0 = D (Slave 変化なし) CLK = 1 の時、 $\overline{CLK} = 0$ 、Slave Q = q0 (Master 変化なし)

クロック信号 (CLK) の立ち上がり (0から1への遷移) の直前のデータ入力 (D) の値が記憶され、出力 (Q) に出力される。

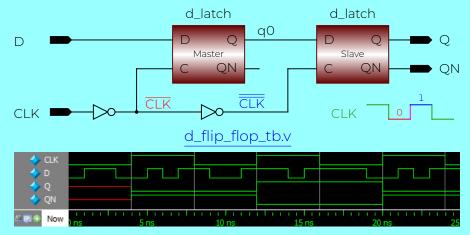

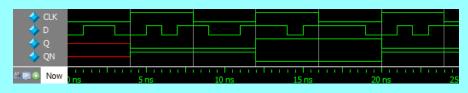

#### DFF シミュレーション

クロック信号 (CLK) の立ち上がり (0から1への遷移) の直前のデータ 入力 (D) の値が記憶され、出力 (Q) に出力される。

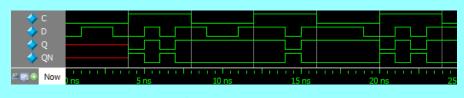

## シミュレーション波形の比較

# Dラッチ

Dフリップフロップ

## シミュレーション波形の比較

Dラッチ

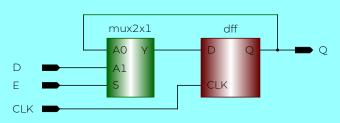

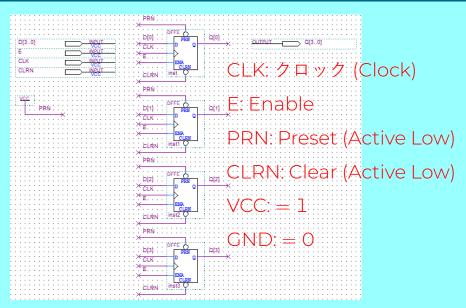

## イネーブル付き DFF (DFFE)

- E = 1: D を選択、DFF に保存

- E = O: Q を選択、DFF に保存 (変化なし)

Quartus II では、DFF と DFFE は直接使用できる

## 4-Bit DFFE (レジスタ)

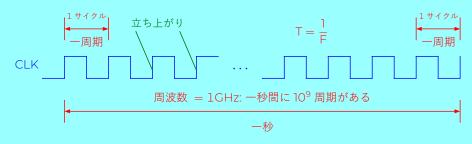

### クロック信号の周波数

周波数

$$F = 1$$

GHz: 一周期の時間  $T = \frac{1}{1 \times 10^9} = 10^{-9}$ s = 1ns

CPU の周波数:4GHz = 4,000,000,000Hz ここには、 $G = 10^9 = 1,000,000,000$

メモリの容量: $16GB = 2^{34}B = 17,179,869,184$  バイト ここには、 $G = 2^{30} = 1,073,741,824 \neq 10^9$

#### JKラッチ

•

$$C = 1, J = 0, K = 0$$

: No change =

•

$$C = 1, J = 0, K = 1$$

: Reset

$$Q_{\text{next}} = J \, \overline{Q} + \overline{K} \, Q$$

K.

$$\bullet$$

C = 1, J = 1, K = 0: Set

•

$$C = 1, J = 1, K = 1$$

: Toggle  $(0 \rightarrow 1 \rightarrow 0 \rightarrow 1 \cdots, 発振)$

•

$$C = 0, J = x, K = x$$

: No change カルノー図からわかること:  $Q_{next} = J \overline{Q} + \overline{K} Q$

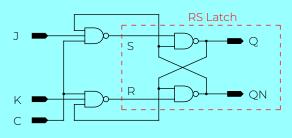

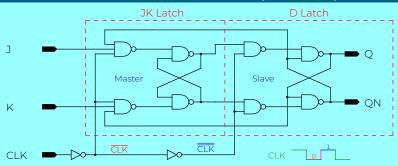

## JK フリップフロップ (JKFF)

CLK = 0 の時、= Master JK Latch (Slave D Latch 変化なし)

CLK = 1 の時、= Slave D Latch (Master JK Latch 変化なし)

CLK の立ち上がりで、 $Q_{next} = J \overline{Q} + \overline{K} Q$

注意:RS ラッチの初期状態がわからないので、Clear などの信号が必要である。

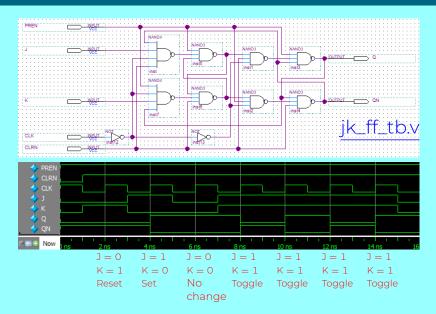

#### JKFF シミュレーション

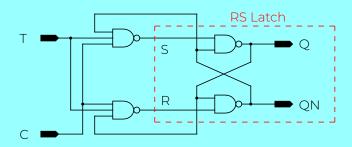

#### | フッチ

#### 回路図からわかること:

$\bullet$  C = 1, T = 0: No change

• C = 1, T = 1: Toggle  $(0 \rightarrow 1 \rightarrow 0 \rightarrow 1 \cdots, 発振)$

$\bullet$  C = 0, T = x: No change

カルノー図からわかること:  $Q_{next} = T\overline{Q} + \overline{T}Q$

$Q_{\text{next}} = T \overline{Q} + \overline{T} Q$

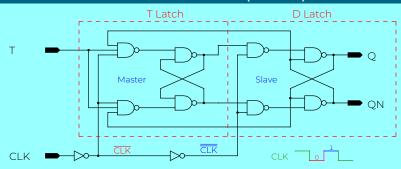

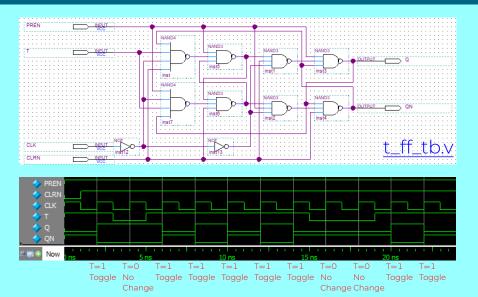

## Tフリップフ<mark>ロップ (TFF</mark>)

CLK = 0 の時、= Master T Latch (Slave D Latch 変化なし)

CLK = 1 の時、= Slave D Latch (Master T Latch 変化なし)

CLK の立ち上がりで、 $Q_{next} = T\overline{Q} + \overline{T}Q$

注意:RS ラッチの初期状態がわからないので、Clear などの信号が必要である。

### TFFシミュレーション

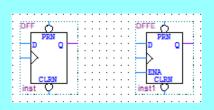

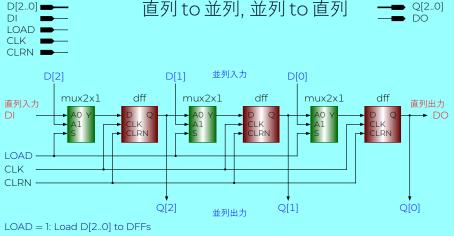

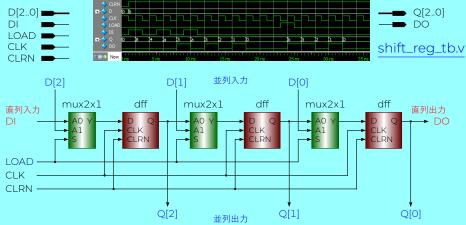

## シフトレジスタ (Shift Register)

LOAD = 0: Shift Right

### シフトレ<u>ジスタのシミュレーション</u>

LOAD = 1: Load D[2..0] to DFFs LOAD = 0: Shift Right

注:実際の回路には 4 ビットの DFF がある。shift\_reg.v を参照してください。

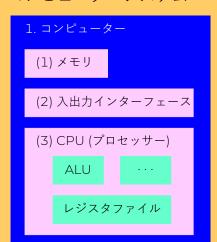

### レジスタファイル (Register File)

#### コンピューターシステム

2. ソフトウェア (OS やコンパイラなど)

3. 入出力デバイス (キーボードやディスプレイなど)

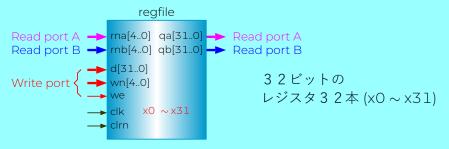

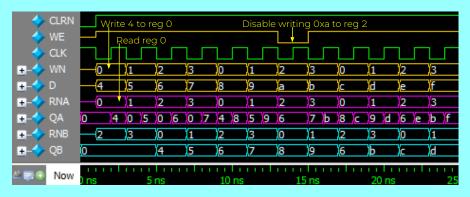

## レジスタファイル (シンボル)

```

rna[4..0] — Register number of read port A (5 bits, 2^5 = 32) rnb[4..0] — Register number of read port B (5 bits, 2^5 = 32) qa[31..0] — Data output of read port A (32 bits) qb[31..0] — Data output of read port B (32 bits) wn[4..0] — Register number of write port (5 bits, 2^5 = 32) d[31..0] — Data input of write port (32 bits) we — Write enable (1 bit)

```

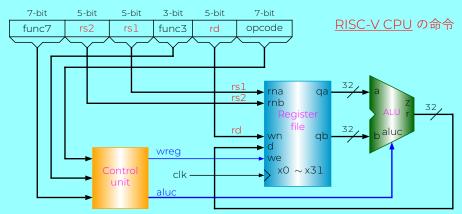

#### レジスタファイルの応用

RISC-V 命令の例

add rd, rs1, rs2 # reg[rd] = reg[rs1] + reg[rs2]

<mark>命令の意味:</mark> レジスタ rsl に格納されている値とレジスタ rs2 に格納されている値を加算して、その結果をレジスタ rd に格納する。

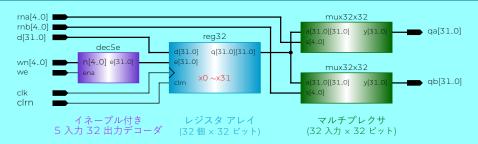

#### レジスタファイルの回路

```

rna[4..0] — Register number of read port A (5 bits, 2^5 = 32)

```

rnb[4..0] — Register number of read port B (5 bits,

$$2^5 = 32$$

)

- qa[31..0] Data output of read port A (32 bits)

- qb[31..0] Data output of read port B (32 bits)

- wn[4..0] Register number of write port (5 bits,  $2^5 = 32$ )

- d[31..0] Data input of write port (32 bits)

- we Write enable (1 bit)

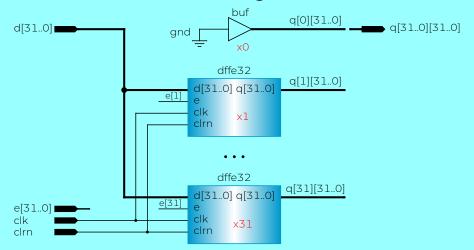

### レジスタアレイの回路

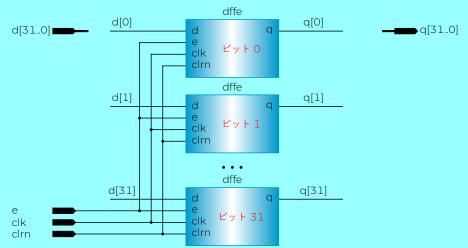

#### 32 個 32 ビットレジスタ reg32:

## レジスタの回路

#### 32 ビットレジスタ dffe32:

### ラッチとフリップフロップ

#### まとめ

- 順序回路

- RS ラッチ (RS Latch)

- D ラッチ (D Latch)

- D フリップフロップ (DFF, DFFE)

- Tフリップフロップ (TFF)

- JK フリップフロップ (JKFF)

- レジスタ (Register)

- レジスタファイル (Register File)

## 課題 XI (100 点)

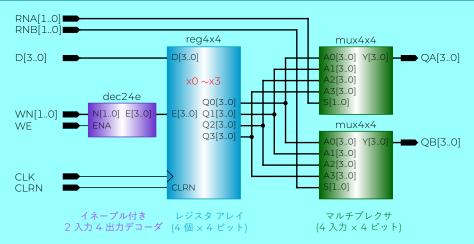

4 × 4 レジスタ・ファイルを回路図で設計し動作検証シミュレーションして下さい。

プロジェクト名は regfile4x4 にすること。 テストベンチ regfile4x4\_tb.v を使って下さい。

## 課題 XI (100 点) 回路図

dec24e · · · · · · · · · · · 第 10 回資料 P8 の dec38e を参照

mux4x4 · · · · · · · · · · · · 第 9 回資料課題 IX 問題 1 を参照

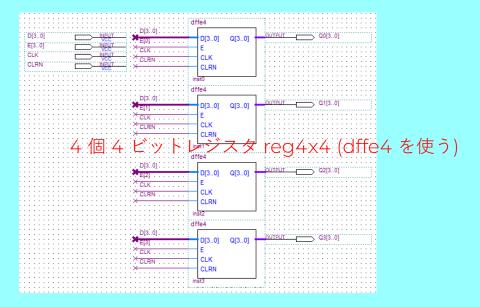

## 課題 XI (100 点) reg4x4.bdf

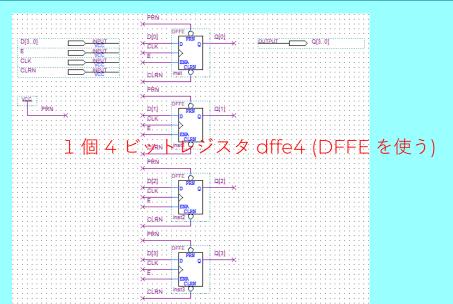

## 課題 XI (100 点) dffe4.bdf

## 課題 XI (100 点) 波形

シミュレーション波形の考察: CLK の立ち上がりで適当な値を各レジスタに保存して、そのあと、各レジスタに保存している値を読み出し確認して下さい。特に、Ons~7nsと13ns~19nsの波形について、説明して下さい。

#### Verilog HDL による課題の実装

#### 1ビット DFF の設計

```

module dff1b (CLK, CLRN, D, Q);

input D;

input CLK, CLRN;

output Q;

Q;

reg

always @(posedge CLK or negedge CLRN) begin

if (!CLRN) begin

Q <= 0;

end else begin

0 \le D:

end

end

endmodule

```

#### Verilog HDL による課題の実装

#### 1ビット DFFE の設計

```

module dffe1b (CLK, CLRN, E, D, Q);

input

D;

input CLK, CLRN, E;

output Q;

reg

always @(posedge CLK or negedge CLRN) begin

if (!CLRN) begin

Q \ll 0;

end else begin

if (E) begin

Q <= D:

end

end

end

endmodule

```

#### Verilog HDL による課題の実装

#### 4ビット DFFE の設計

```

module dffe4b (CLK, CLRN, E, D, Q);

input [3:0] D;

input CLK, CLRN, E;

output [3:0] Q;

reg [3:0] Q;

always @(posedge CLK or negedge CLRN) begin

if (!CLRN) begin

Q <= 0;

end else begin

if (E) begin

Q <= D:

end

end

end

endmodule

```

#### Verilog HDL による課題の実装

4個4ビットレジスタの設計(P31を参照)

```

module dffe4bx4 (CLK, CLRN, E, D, Q0, Q1, Q2, Q3);

input [3:0] D;

input CLK, CLRN;

input [3:0] E;

output [3:0] Q0, Q1, Q2, Q3;

dffe4b i0 (CLK, CLRN, E[0], D, Q0); // reg 0

dffe4b i1 (

); // reg 1

dffe4b i2 (

); // reg 2

dffe4b i3 (

); // reg 3

endmodule

```

上記コードを完成しシミュレーションして下さい。

#### Verilog HDL による課題の実装

4個4ビットレジスタ・ファイルの設計(P30を参照)

```

module regfile4x4b (CLK, CLRN, WE, D, WN, RNA, RNB, QA, QB);

input [3:0] D;

input [1:0] RNA, RNB, WN;

input CLK, CLRN, WE;

output [3:0] QA, QB;

wire [3:0] ENA;

wire [3:0] Q0, Q1, Q2, Q3;

dec24ena i0 (WN, WE, ENA); // 2-4 decoder with enable

dffe4bx4 i1 (CLK, CLRN, ENA, D, Q0, Q1, Q2, Q3);

mux4x4b i2 (

); // output QA

m_{11}x_4x_4b i3 (

); // output QB

endmodule

```

上記コードを完成しシミュレーションして下さい。

#### 32個32ビット RISC-V レジスタ・ファイルの設計

```

module regfile32x32 (rs1, rs2, d, rd, we, clk, rst_n, q1, q2);

input [31:0] d;

// data to be written

input [4:0] rs1, rs2, rd; // RISC-V register numbers

input clk, rst_n, we; // we: write enable

output [31:0] q1, q2; // two outputs

reg [31:0] x [1:31]; // 31 registers, x[0] = 0

assign q1 = (rs1 == 0) ? 0 : x[rs1]; // read port 1

assign q2 = (rs2 == 0) ? 0 : x[rs2]; // read port 2

integer i;

always @(posedge clk or negedge rst_n)

if (!rst n)

// active low reset

for (i = 1; i < 32; i = i + 1) // in parallel

x[i] <= 0;

// clear all registers

else

if ((rd != 0) && we)

x[rd] \le d:

// write port

endmodule

```