## 論理回路入門(8)

2進数の掛け算とウォレスツリー

李 亜民

2022年11月15日(火)

## 2進数の掛け算

#### ポイント

- 符号なし数の掛け算(乗算)

- 符号なし乗算器回路

- 符号なし CSAs を使用する乗算器回路

- 符号なしのウォレスツリー乗算器

- 2の補数で表現する数の掛け算

- 2の補数のウォレスツリー乗算器

# 2進数掛け算の方式と掛け算命令

- 直列掛け算

- ▶筆算と同じ、各桁を順次計算。

- ② 並列掛け算

- ▶組合わせ論理回路を利用、各桁を同時に計算。

- ROM 利用の掛け算

- ▶ ROM にデータを用意、演算時に読み出し。

#### CPU の掛け算命令の例(32 ビット×32 ビット)

- mulh · · · · · · 64 ビット積の上位 32 ビットの計算

- mul·····64 ビット積の下位 32 ビットの計算

2倍のビット数が必要

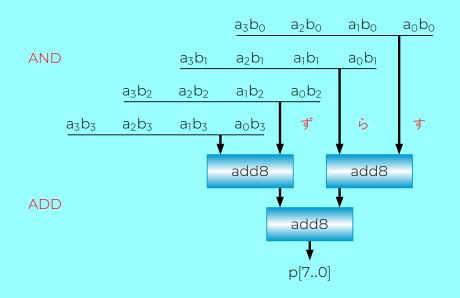

## 符号なし数の乗算器回路

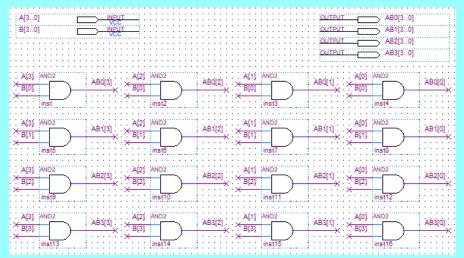

#### and2\_4x4.bdf

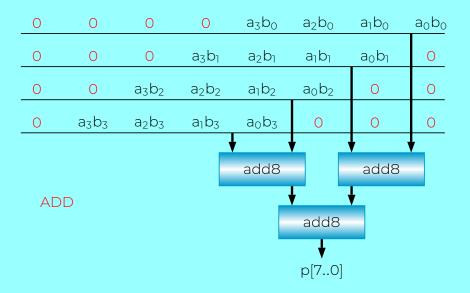

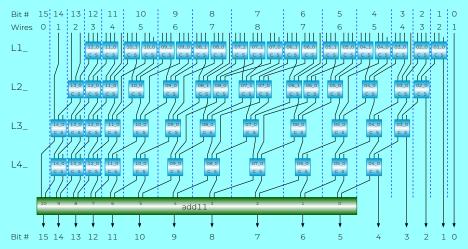

## 符号なし数の乗算器回路

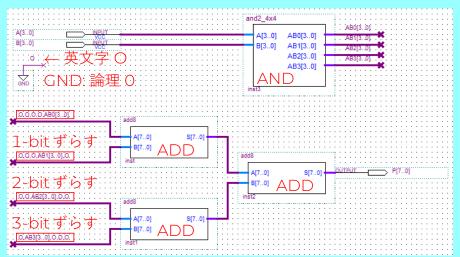

#### mul4x4\_tree.bdf

#### テストベンチ

#### 回路のモジュール mul4x4\_tree を呼び出し、入力のパターンを用意する。

```

'timescale 1ns/1ps // unit = 1 ns; accuracy = 1 ps

module mul4x4_tree_tb;

reg [3:0] A,B;

wire [7:0] P:

mul4x4_tree i1 (.A(A), .B(B), .P(P));

integer i,j;

initial begin

\#0 A = 0; B = 0;

for (i = 0; i < 16; i = i + 1) begin

for (j = i; j < 16; j = j + 1) begin

#1 A = i; B = j;

end

end

#1 $stop;

end

endmodule

```

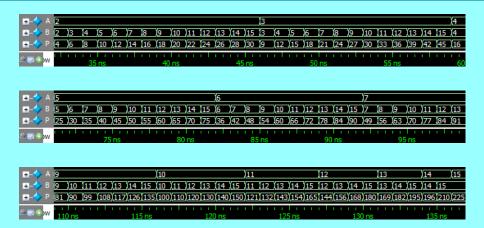

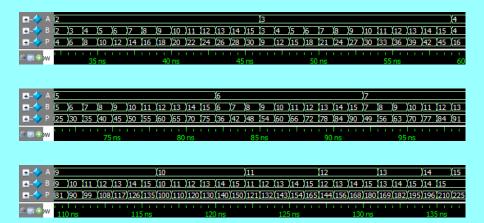

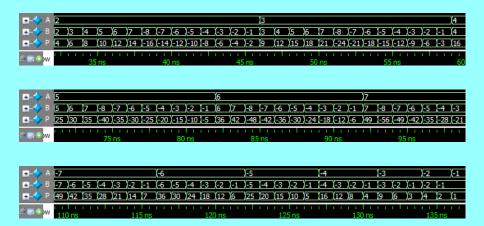

### 乗算器回路のシミュレーション

$\uparrow$

Radix: Unsigned (符号なし)

$15 \times 15 = 225$

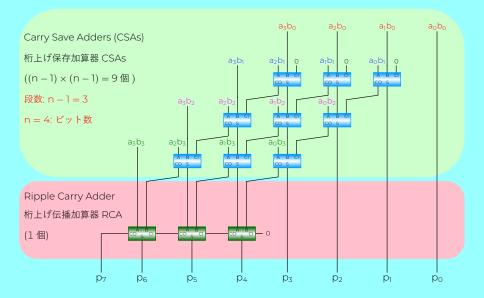

## CSA を使用する乗算器回路 (4 ビット)

#### Wallace Tree (ウォレスツリー)

計算可能であれば、大量のCSAを使用して並列に計算する。

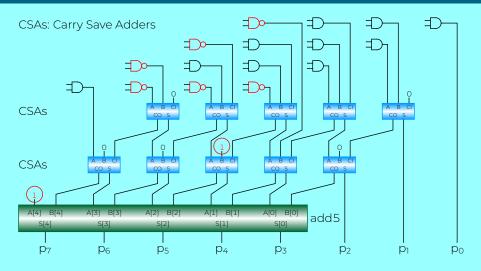

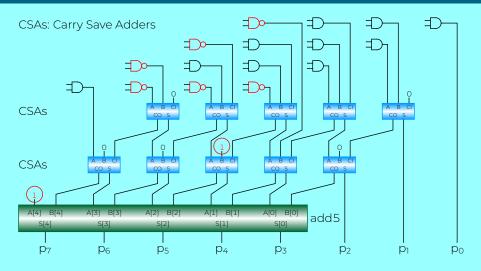

## Wallace Tree の回路

#### mul4x4\_wallace\_tree.bdf

注意: 一部のワイヤーが省略された。

#### テストベンチ

```

'timescale 1ns/1ps // unit = 1 ns; accuracy = 1 ps

module mul4x4_wallace_tree_tb;

reg [3:0] A,B;

wire [7:0] P;

mul4x4_wallace_tree i1 (.A(A), .B(B), .P(P));

integer i, j;

initial begin

\#0 A = 0; B = 0;

for (i = 0; i < 16; i = i + 1) begin

for (j = i; j < 16; j = j + 1) begin

#1 A = i; B = j;

end

end

#1 $stop;

end

endmodul e

```

## Wallace Tree の波形

Radix: Unsigned (符号なし)

$15 \times 15 = 225$

# Wallace Tree (8ビット)

```

Level 1 (L1) carry save adders (CSAs)

a[6] a[5] a[4] a[3]

a[2]

CSA: 3 inputs \rightarrow 2 outputs

b[6] b[5] b[4]

b[3]

b[2]

a \times b[0] -

a \times b[1]

a \times b[2]

a \times b[3]

a \times b[4]

a \times b[5] -

To I2

a \times b[6] ——

a \times b[7] \rightarrow

Bit number

10

# of wires (*)

# of CSAs

0

```

段 1 (L1) の CSAs (# of CSAs: CSA の個数) まるアスタリスク: 段 2 (L2) に送る。

計算可能であれば、大量のCSAを使用して並列に計算する。

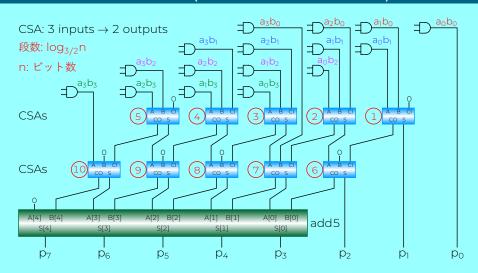

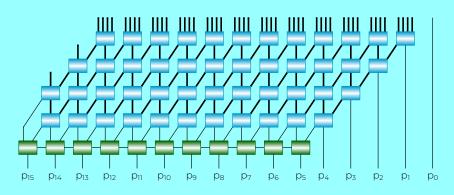

## Wallace Tree (8ビット)

CSA: 3 inputs  $\rightarrow$  2 outputs;

段数 = log<sub>3/2</sub>n

計算可能であれば、大量の CSA を使用して並列に計算する。

## Wallace Tree (8ビット)

綺麗に整列されたウォレスツリーの回路図。 詳細については、前のページを参照してください。

4段CSAs

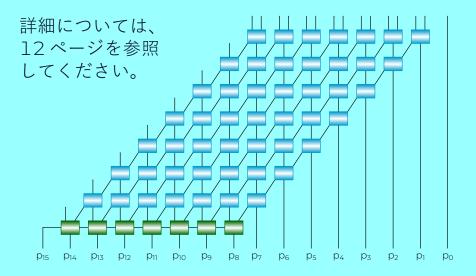

# CSA を使用する乗算器回路 (8 ビット)

7段CSAs

● 符号なし数の掛け算

$$1111 \times 1111 = 1110\underline{0001} \cdot \dots \cdot 15 \times 15 = 225$$

$1111 \times 0010 = 0001\underline{1110} \cdot \dots \cdot 15 \times 2 = 30$

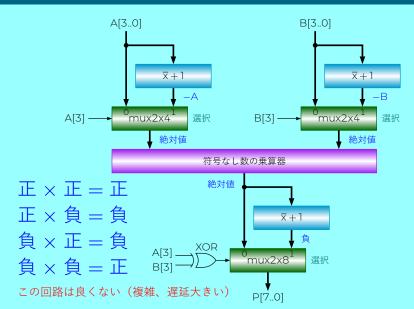

● 2の補数で表現する数の掛け算

$$1111 \times 1111 = 0000\underline{0001} \cdot \cdot \cdot \cdot \cdot (-1) \times (-1) = +1$$

$1111 \times 0010 = 1111\underline{1110} \cdot \cdot \cdot \cdot \cdot (-1) \times (+2) = -2$

● 2の補数掛け算のルール

$$\overline{\mathbb{E}} \times \overline{\mathbb{E}} = \overline{\mathbb{E}}$$

赤:下位4ビットは同じである

青:下位4ビットは同じである

$$-X = \overline{X} + 1$$

$xov{c}$

$$\begin{aligned} &(-a_3\times B_3)\times {\color{red}2^3}=(\overline{0},\overline{0},\overline{a_3b_2},\overline{a_3b_1},\overline{a_3b_0}+1)\times {\color{red}2^3}\\ &(-b_3\times A_3)\times {\color{red}2^3}=(\overline{0},\overline{0},\overline{a_2b_3},\overline{a_1b_3},\overline{a_0b_3}+1)\times {\color{red}2^3} \end{aligned}$$

#### つまり

| Bit# | 7 | 6 | 5                   | 4                             | 3                   |    |

|------|---|---|---------------------|-------------------------------|---------------------|----|

|      | 1 | 1 | $\overline{a_3b_2}$ | a <sub>3</sub> b <sub>1</sub> | $\overline{a_3b_0}$ | 反転 |

|      | 0 | O | 0                   | Ο                             | 1                   | +1 |

|      | 1 | 1 | $\overline{a_2b_3}$ | $\overline{a_1b_3}$           | $\overline{a_0b_3}$ | 反転 |

| +    | 0 | O | 0                   | 0                             | 1                   | +1 |

| Bit# | 7 | 6 | 5                   | 4                             | 3                   |    |

|------|---|---|---------------------|-------------------------------|---------------------|----|

|      | 1 | 1 | $\overline{a_3b_2}$ | a <sub>3</sub> b <sub>1</sub> | $\overline{a_3b_0}$ | 反転 |

|      | 0 | O | 0                   | 0                             | 1                   | +1 |

|      | 1 | 1 | $\overline{a_2b_3}$ | $\overline{a_1b_3}$           | $\overline{a_0b_3}$ | 反転 |

| +    | 0 | 0 | 0                   | 0                             | 1                   | +1 |

整理

| Bit# | 7 | 6 | 5                   | 4                   | 3                   |

|------|---|---|---------------------|---------------------|---------------------|

|      | 0 | 0 | $\overline{a_3b_2}$ | $\overline{a_3b_1}$ | $\overline{a_3b_0}$ |

|      | 0 | Ο | $\overline{a_2b_3}$ | $\overline{a_1b_3}$ | $\overline{a_0b_3}$ |

| +    | 1 | Ο | 0                   | 1                   | Ο                   |

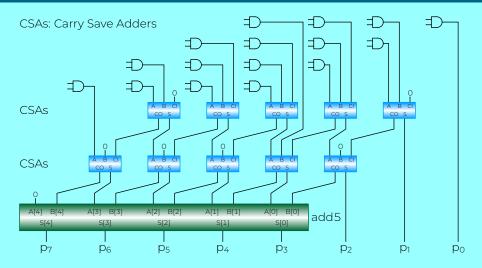

## 2の補数のウォレスツリーの回路

a<sub>3</sub>b<sub>2</sub>、a<sub>3</sub>b<sub>1</sub>、a<sub>3</sub>b<sub>0</sub>、a<sub>2</sub>b<sub>3</sub>、a<sub>1</sub>b<sub>3</sub>、a<sub>0</sub>b<sub>3</sub>:P6 を参照

#### テストベンチ

```

'timescale 1ns/1ps // unit = 1 ns; accuracy = 1 ps

module mul4x4_wallace_tree_signed_tb;

reg [3:0] A,B;

wire [7:0] P;

mul4x4_wallace_tree_signed i1 (.A(A), .B(B), .P(P));

integer i, j;

initial begin

\#0 A = 0; B = 0;

for (i = 0; i < 16; i = i + 1) begin

for (j = i; j < 16; j = j + 1) begin

#1 A = i; B = j;

end

end

#1 $stop;

end

endmodul e

```

## 2の補数のウォレスツリーの波形

$\uparrow$

Radix: Decimal (符号付き 10 進)  $(-1) \times (-1) = +1$

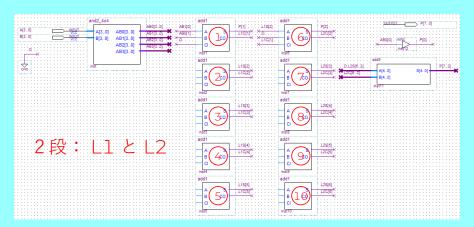

## 符号なしのウォレスツリーの回路

$a_3b_2$ 、 $a_3b_1$ 、 $a_3b_0$ 、 $a_2b_3$ 、 $a_1b_3$ 、 $a_0b_3$ :P6 を参照

## 2の補数のウォレスツリーの回路

a<sub>3</sub>b<sub>2</sub>、a<sub>3</sub>b<sub>1</sub>、a<sub>3</sub>b<sub>0</sub>、a<sub>2</sub>b<sub>3</sub>、a<sub>1</sub>b<sub>3</sub>、a<sub>0</sub>b<sub>3</sub>:P6 を参照

## 2進数の掛け算

#### まとめ

- 符号なし数の掛け算(乗算)

- 符号なし乗算器回路

- 符号なし CSAs を使用する乗算器回路

- 符号なしのウォレスツリー乗算器

- 2の補数で表現する数の掛け算

- 2の補数のウォレスツリー乗算器

# 課題 VIII (100 点 + 200 点)

4 ビット×4 ビット<mark>符号なし</mark>のウォレスツリーを設計し動作検証 シミュレーションして下さい。

プロジェクト名は mul4x4\_wallace\_tree にすること。 テストベンチ <u>mul4x4\_wallace\_tree\_tb.v</u> を使って下さい。

```

オプション (+50 点): 4 ビット \times 4 ビット 2 の補数のウォレスツリーを設計し動作検証シミュレーションして下さい。(注意:gnd = 0; vcc = 1) プロジェクト名は mul4x4_wallace_tree_signed にすること。テストベンチ mul4x4_wallace_tree_signed_tb.v を使って下さい。

```

# 課題 VIII (100 点 + 200 点)

オプション (+100 点): 8 ビット  $\times$  8 ビット  $\frac{6}{5}$  そのウォレスツリーを設計し動作検証シミュレーションして下さい。

プロジェクト名は mul8x8\_wallace\_tree にすること。 テストベンチを自分で作って下さい。

オプション (+50 点): 8 ビット  $\times$  8 ビット 2 の補数のウォレスツリーを設計し動作検証シミュレーションして下さい。(注意:gnd = 0; vcc = 1) プロジェクト名は mul8x8\_wallace\_tree\_signed にすること。テストベンチを自分で作って下さい。

## Verilog HDL による課題の実装

5ビット加算器の設計(第6回資料P14を参照)

```

module add5b (A, B, S);

input [4:0] A, B;

output [4:0] S;

wire [4:0] c; // internal wires

add1b i0 (A[0], B[0], 1'b0, c[0], S[0]); // full adder 0

add1b i1 (A[1], B[1], c[0], c[1], S[1]); // full adder 1

add1b i2 (A[2], B[2], c[1], c[2], S[2]); // full adder 2

add1b i3 (A[3], B[3], c[2], c[3], S[3]); // full adder 3

add1b i4 (A[4], B[4], c[3], c[4], S[4]); // full adder 3

endmodule

```

#### Verilog HDL による課題の実装 AND2 マトリクス(行列)(P8 を参照)

```

module and4x4 (A, B, ABO, AB1, AB2, AB3);

input [3:0] A, B;

output [3:0] ABO, AB1, AB2, AB3;

assign ABO = A & \{4\{B[0]\}\};

assign AB1 = A & \{4\{B[1]\}\};

assign AB2 = A & \{4\{B[2]\}\};

assign AB3 = A & \{4\{B[3]\}\};

endmodule

```

#### Verilog HDL による課題の実装

符号なしのウォレスツリーの回路(P13、P14を参照)

```

module wallace4x4 (A, B, P);

input [3:0] A, B;

output [7:0] P;

wire [3:0] ABO, AB1, AB2, AB3;

wire [5:1] L1C;

wire [5:2] L1S;

wire [6:2] L2C;

wire [6:3] L2S;

and4x4 iO (A, B, ABO, AB1, AB2, AB3);

assign P[0] = ABO[0];

add1b i1 (AB1[0], AB0[1], 1'b0, L1C[1], P[1]); // 1 L1

```

#### Verilog HDL による課題の実装

符号なしのウォレスツリーの回路(P13、P14を参照)

```

add1b i2 (AB2[0], AB1[1], AB0[2], L1C[2], L1S[2]); // 2 L1 add1b i3 ( , , , L1C[3], L1S[3]); // 3 L1 add1b i4 ( , , , L1C[4], L1S[4]); // 4 L1 add1b i5 ( , , , L1C[5], L1S[5]); // 5 L1 add1b i6 (L1S[2], L1C[1], 1'b0, L2C[2], P[2]); // 6 L2 add1b i7 ( , , , L2C[3], L2S[3]); // 7 L2 add1b i8 ( , , , L2C[4], L2S[4]); // 8 L2 add1b i9 ( , , , L2C[5], L2S[5]); // 9 L2 add1b ia ( , , , L2C[6], L2S[6]); // 10 L2 add5b ib ({1'b0,L2S[6:3]}, L2C[6:2], P[7:3]); // add5b endmodule

```

上記コードを完成しシミュレーションして下さい。

Sを符号なしの4ビットAかける4ビットBの8ビット積とする

$$A_3A_2A_1A_0 \times B_3B_2B_1B_0 = S_7S_6S_5S_4S_3S_2S_1S_0$$

Tを2の補数の4ビットAかける4ビットBの8ビット積とする

$$A_3A_2A_1A_0 \times B_3B_2B_1B_0 = T_7T_6T_5T_4T_3T_2T_1T_0$$

証明:

$$S_3S_2S_1S_0 = T_3T_2T_1T_0$$