### コンピュータ構成と設計 (6) <sup>単一サイクル</sup> CPU 設計

李 亜民

2024年11月7日(木)

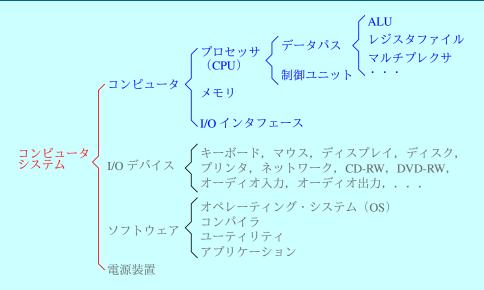

#### コンピュータとコンピュータシステム

### 20 RISC-V 命令のまとめ

```

1. add rd, rs1, rs2 # rd <- rs1 + rs2

2. sub rd, rs1, rs2 # rd <- rs1 - rs2

3. slt rd, rs1, rs2 # rd <- rs1 < rs2 (signed)

4. xor rd, rs1, rs2 # rd <- rs1 ^ rs2

5. or rd, rs1, rs2 # rd <- rs1 | rs2

6. and rd, rs1, rs2 # rd <- rs1 & rs2

7. slli rd, rs1, shamt

# rd <- rs1 << shamt

8. srli rd, rs1, shamt # rd <- rs1 >> shamt

9. srai rd, rs1, shamt

# rd <- rs1 >>>shamt

10. jalr rd, rs1, imm # rd <- pc+4; pc <- rs1+imm

11. addi rd, rs1, imm # rd <- rs1 + imm

12. xori rd, rs1, imm # rd <- rs1 ^ imm

13. ori rd, rs1, imm # rd <- rs1 | imm

14. andi rd, rs1, imm # rd <- rs1 & imm

15. lw rd, imm(rs1) # rd <- memory[rs1+imm]

16. sw rs2, imm(rs1) # memory[rs1+imm] <- rs2

17. beg rs1, rs2, label # if (rs1==rs2) pc <- label

18. bne rs1, rs2, label # if (rs1!=rs2) pc <- label

19. jal rd, label # rd <- pc+4; pc <- label

20. lui rd. imm # rd <- imm.000000000000

```

# **RV32I Base Instruction Set Encoding**

| 31 25                 | 24 20 | 19 15 | 14 12 | 11 7        | 6 0     |

|-----------------------|-------|-------|-------|-------------|---------|

| 0000000               | rs2   | rs1   | 000   | rd          | 0110011 |

| 0100000               | rs2   | rs1   | 000   | rd          | 0110011 |

| 0000000               | rs2   | rs1   | 010   | rd          | 0110011 |

| 0000000               | rs2   | rs1   | 100   | rd          | 0110011 |

| 0000000               | rs2   | rs1   | 110   | rd          | 0110011 |

| 0000000               | rs2   | rs1   | 111   | rd          | 0110011 |

| 0000000               | shamt | rs1   | 001   | rd          | 0010011 |

| 0000000               | shamt | rs1   | 101   | rd          | 0010011 |

| 0100000               | shamt | rs1   | 101   | rd          | 0010011 |

| imm[11:0]             |       | rs1   | 000   | rd          | 1100111 |

| imm[11:0]             |       | rs1   | 000   | rd          | 0010011 |

| imm[11                | :0]   | rs1   | 100   | rd          | 0010011 |

| imm[11                | :0]   | rs1   | 110   | rd          | 0010011 |

| imm[11                | :0]   | rs1   | 111   | rd          | 0010011 |

| imm[11:0]             |       | rs1   | 010   | rd          | 0000011 |

| imm[11:5]             | rs2   | rs1   | 010   | imm[4:0]    | 0100011 |

| imm[12 10:5]          | rs2   | rs1   | 000   | imm[4:1 11] | 1100011 |

| imm[12 10:5]          | rs2   | rs1   | 001   | imm[4:1 11] | 1100011 |

| imm[20 10:1 11 19:12] |       |       |       | rd          | 1101111 |

| imm[31:12]            |       |       |       | rd          | 0110111 |

add 1. sub slt xor or and 7. slli srli 9. srai 10. jalr addi 11. 12. xori 13. ori 14. andi 15. lw 16. SW 17. beq 18. bne 19. jal 20. lui

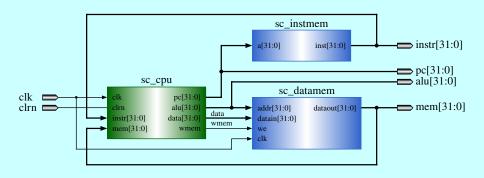

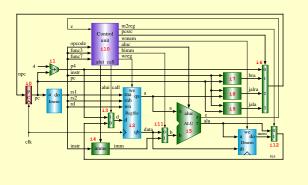

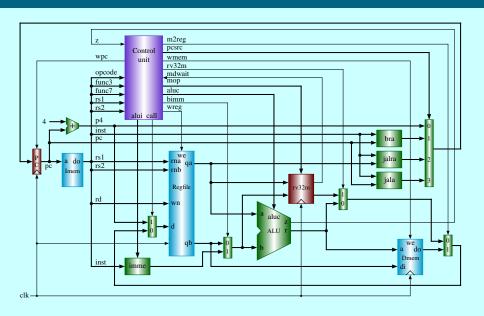

#### RISC-V コンピュータ

CPU + 命令メモリ Imem + データメモリ Dmem

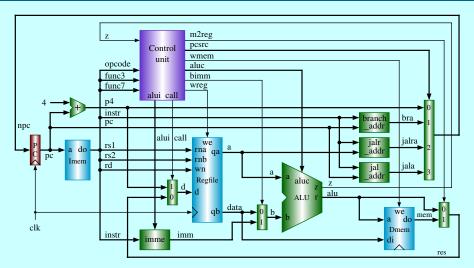

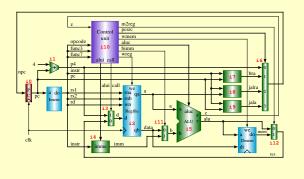

#### RISC-V CPU とメモリの回路

単一サイクル RISC-V CPU + 命令メモリ + データメモリ

# RISC-V sc\_computer の回路

```

'timescale 1ns/1ns

module sc computer(clk.

sc instmem

clrn.

alu.

a[31:0] i1 inst[31:0]

instr[31:0]

instr.

mem,

pc[31:0]

DC

alu[31:0]

sc cpu

sc datamem

pc[31:0]

clk =

clk:

input

mem[31:0]

clrn =

alu[31:0]

addr[31:0]

dataout[31:0]

input

clrn:

datain[31:0]

nstr[31:0]

data[31:0]

output Γ31:07 alu:

nem[31:0]

i2

output [31:0] instr;

clk

output [31:0] mem:

output [31:0] pc:

wire

wmem:

Γ31:0] data;

wire

sc_cpu

i0 (.clk(clk),

.clrn(clrn).

.instr(instr).

.mem(mem),

.wmem(wmem).

.alu(alu),

.data(data).

.pc(pc));

sc instmem i1 (.a(pc).

.inst(instr));

sc_datamem i2 (.we(wmem), // .we: signal of sc_datamem; wmem: wire of sc_computer

.clk(clk),

.addr(alu).

.datain(data),

.dataout(mem)):

endmodule

```

```

'timescale 1ns/1ns

module sc_cpu (

clk.

clrn.

instr.

mem.

wmem.

alu.

data.

wmem

unit

aluc

110

bimm

alui call

input

clk;

clrn;

input

input [31:0] instr;

input [31:0] mem;

output

wmem;

output [31:0] alu;

output [31:0] data;

output [31:0] pc;

[31:0] a;

wire

wire

[31:0] b;

[3:0] aluc;

wire

[1:0] alui;

wire

bimm;

wire

wire

[31:0] bra:

wire

calí;

wire

[31:0] d:

wire

Γ31:07 imm:

wire

[31:0] jala;

wire

[31:0] ialra:

```

```

wire

m2reg:

[31:0] npc:

wire

wire

[31:0] p4;

wire

[1:0] pcsrc:

[31:0] res;

wire

wire

wreg:

wire

z:

dff32 i0 (

Control

wmem

.clk(clk).

unit

aluc

.clrn(clrn),

110

bimm

.d(npc),

alui call

.q(pc));

pc4

.pc(pc),

.p4(p4));

sc_cu i10 (

.z(z),

.func3(instr[14:12]),

.func7(instr[31:25]),

.opcode(instr[6:0]),

.m2reg(m2reg),

.bimm(bimm),

.call(call),

.wreg(wreg),

.wmem(wmem),

.aluc(aluc),

.alui(alui).

.pcsrc(pcsrc)):

```

```

mux2x32 i11 (

.s(bimm).

.a0(data),

.a1(imm).

.y(b));

mux2x32 i12 (

.s(m2reg),

.a0(alu).

.a1(mem),

.y(res));

alu i5 (

.a(a),

.aluc(aluc),

.b(b),

.z(z),

.r(alu));

regfile i2 (

.we(wreg),

.clk(clk),

.clrn(clrn),

.d(d),

.rna(instr[19:15]),

.rnb(instr[24:20]),

.wn(instr[11:7]),

.ga(a),

.qb(data));

```

```

mux2x32 i3 (

.s(call).

.a0(res).

.a1(p4).

.y(d));

imme i4 (

.alui(alui).

.inst(instr).

.imm(imm)):

mux4x32 i6 (

.a0(p4),

.a1(bra),

.a2(jalra),

.a3(jala),

.s(pcsrc),

.y(npc));

branch_addr i7 (

.inst(instr),

.pc(pc),

.addr(bra));

jalr_addr i8 (

.inst(instr),

.rs1(a),

.addr(jalra));

ial addr i9 (

.inst(instr),

.pc(pc).

.addr(jala));

endmodule

```

#### メモリ容量

- メモリ: コンピュータ内でデータやプログラムを記憶する装置

- メモリ容量はバイトで表される。1バイトは8ビットに等しい

- 例えば、"メイン・メモリの容量は16ギガ・バイトである"という感じに使う

| 単位     | 10 進法での意味 | 2進法での意味                          |

|--------|-----------|----------------------------------|

| K (キロ) | $10^{3}$  | $2^{10} = 1\ 024$                |

| М (メガ) | $10^{6}$  | $2^{20} = 1\ 048\ 576$           |

| G (ギガ) | $10^{9}$  | $2^{30} = 1\ 073\ 741\ 824$      |

| T (テラ) | $10^{12}$ | $2^{40} = 1\ 099\ 511\ 627\ 776$ |

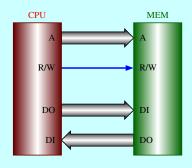

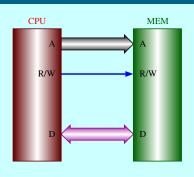

#### メモリとCPU

(a) 独立の単方向データバス

A (Address): アドレスバス D (Data): データバス DI (Data In): データバス

DO (Data Out): データバス

R/W (Read/Write): リード/ライト信号

(b) 単一の双方向データバス

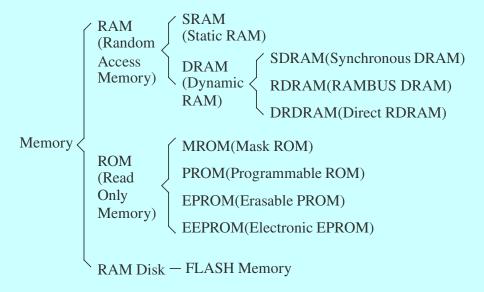

#### メモリの種類

# 命令メモリ (テスト・プログラム)

```

'timescale Ins/Ins

module sc instmem (a.inst):

input [31:0] a;

output [31:0] inst:

wire [31:0] rom [0:31]:

// (pc)

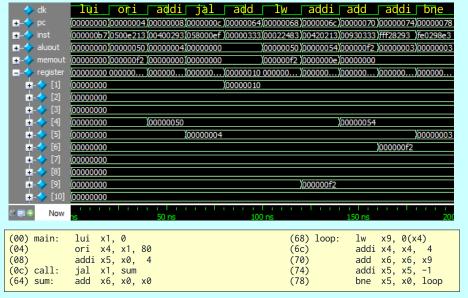

assign rom[5'h00] = 32'b000000000000000000000010110111; // (00) main:

# x1 <- 0

lui x1, 0

assign rom[5'h01] = 32'b00000101000000001110001000010011; // (04)

ori x4, x1, 80

# x1 <- 80

assign rom[5'h02] = 32'b000000000100000000001010010011: // (08)

addi x5. x0. 4

# v5 <- 4

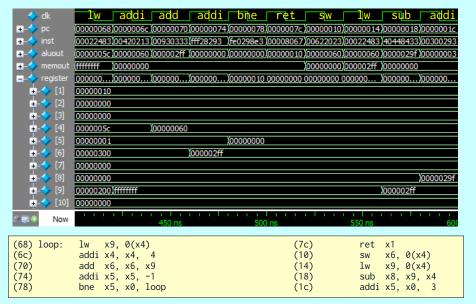

assign rom[5'h03] = 32'b0000010110000000000000011101111: // (0c) call:

ial x1. sum

# x1 <- 0x10 (return address), call sum

assign_rom[5'h04] = 32'h0000000001100010001000000100011: // (10)

sw x6. 0(x4)

# memory[x4+0] <- x6

assign rom[5'h05] = 32'b00000000000000100010010010000011; // (14)

lw x9, 0(x4)

# x6 <- memory[x4+0]

assign rom[5'h06] = 32'b01000000010001000010000110011: // (18)

sub x8, x9, x4

# v8 <- v9 - v4

assign rom[5'h07] = 32'b0000000000110000000001010010011: // (1c)

addi x5. x0. 3

# v5 <- 3

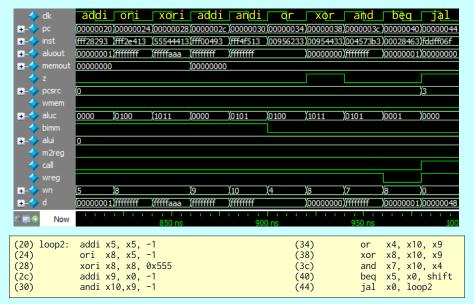

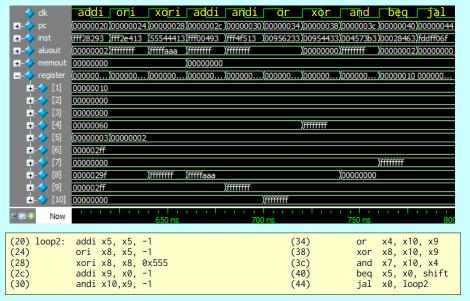

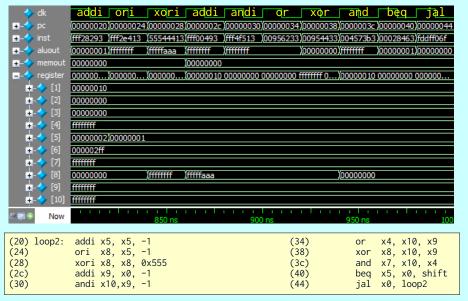

assign_rom[5'h08] = 32'h111111111111110010100001010010011: // (20) loop2:

addi x5. x5. -1

# x5 <- x5 - 1

assign rom[5'h09] = 32'b111111111111100101110010000010011; // (24)

ori x8, x5, -1

# x8 <- x5 | 0xffffffff = 0xfffffffff

xori x8, x8, 0x555 # x8 <- x8 ^ 0x00000555 = 0xfffffaaa

assign rom[5'h0a] = 32'b010101010101010001000100010011: // (28)

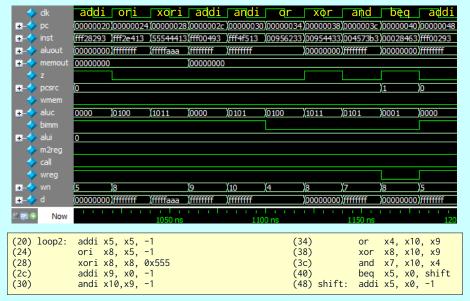

assign rom[5'h0b] = 32'b111111111111100000000010010010011: // (2c)

addi x9. x0. -1

# x9 <- 0xffffffff

assign_rom[5'h0c] = 32'b11111111111111010011111010100010011: // (30)

andi x10.x9. -1

# x10<- x9 & 0xffffffff = 0xfffffffff

assign rom[5'h0d] = 32'b000000001001010110001000110011; // (34)

or x4, x10, x9

# x4 <- x10 \mid x9 = 0xfffffffff

assign rom[5'h0e] = 32'b00000000100101010100010000110011: // (38)

xor x8, x10, x9

# x8 <- x10 ^ x9 = 0x000000000

assign rom[5'h0f] = 32'b00000000010001010111001110110011: // (3c)

and x7, x10, x4

assign rom[5'h10] = 32'h0000000000000101000110001100011: // (40)

beq x5, x0, shift # if x5 = 0, goto shift

assign rom[5'h11] = 32'b111111011101111111111000001101111; // (44)

jal x0, loop2

# jump loop2

assign rom[5'h12] = 32'b11111111111111000000000001010010011: // (48) shift: addi x5, x0, -1

# x5 <- 0xffffffff

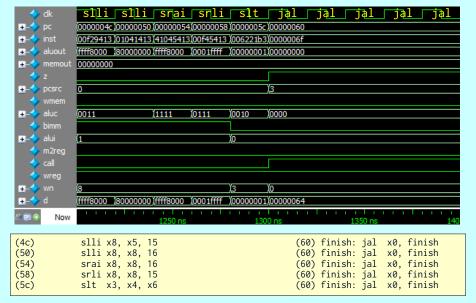

assign rom[5'h13] = 32'b00000000111100101001010000010011: // (4c)

slli x8, x5, 15

# x8 <- 0xffffffff << 15 = 0xffff8000

assign_rom[5'h14] = 32'h000000010000010100001010000010011: // (50)

slli x8, x8, 16

# x8 <- 0xffff8000 << 16 = 0x80000000

assign rom[5'h15] = 32'b010000010000010101010000010011; // (54)

srai x8. x8. 16

# x8 <- 0x80000000 >>> 16 = 0xffff8000

# v8 <- 0vffff8000 >> 15 = 0v0001ffff

assign rom[5'h16] = 32'b00000000111101000101010000010011: // (58)

srli x8. x8. 15

assign rom[5'h17] = 32'b00000000011000100010000110110011: // (5c)

slt x3, x4, x6

# x3 <- 0xffffffff < 0x000002ff = 1

assign rom[5'h18] = 32'b0000000000000000000000001101111: // (60) finish: ial x0. finish

# dead loop

assign rom[5'h19] = 32'b000000000000000000001100110011; // (64) sum:

add x6. x0. x0

# x6 <- 0 (subroutine entry)

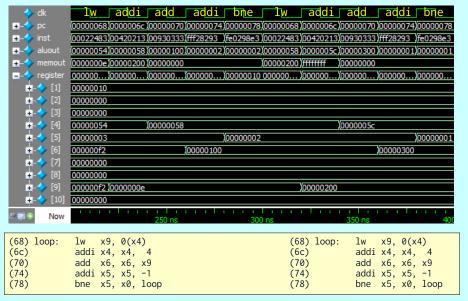

assign rom[5'h1a] = 32'b0000000000000010010010010000011: // (68) loop:

lw x9. 0(x4)

# x9 <- memorv[x4+0]

assign rom[5'h1b] = 32'b000000000100001000001000010011: // (6c)

addi x4, x4, 4

# x4 <- x4 + 4 (address+4)

assign rom[5'h1c] = 32'b00000000100100110000001100110011: // (70)

add x6, x6, x9

\# x6 < -x6 + x9 (sum)

addi x5. x5. -1

# x5 <- x5 - 1 (counter--)

assign rom[5'h1d] = 32'h1111111111111001010000010100100111: // (74)

assign rom[5'h1e] = 32'b111111110000000101001100011100011; // (78)

bne x5, x0, loop # if x5 != 0, goto loop

assign rom[5'h1f] = 32'b000000000000000000000001100111: // (7c)

ret v1

# return from subroutine

assign inst = rom[a[6:2]]:

sc instmem.s.txt

endmodule

```

# データメモリ (テスト・データ)

```

'timescale 1ns/1ns

module sc_datamem (addr,datain,we,clk,dataout); // data memory, ram

// clock

input clk:

input we;

// write enable

input [31:0] datain:

// data in (to memory)

input [31:0] addr;

// ram address

// data out (from memory)

output [31:0] dataout;

reg [31:0] ram [0:31];

// ram cells: 32 words * 32 bits

assign dataout = ram[addr[6:2]];

// use word address to read ram

always @ (posedge clk)

if (we) ram[addr[6:2]] = datain; // use word address to write ram

integer i:

initial begin

// initialize memory

for (i = 0; i < 32; i = i + 1)

ram[i] = 0:

// ram[word addr] = data

// (byte_addr) item in data array

ram[5'h14] = 32'h000000f2:

// (50) data[0]

ram[5'h15] = 32'h0000000e;

// (54) data[1]

ram[5'h16] = 32'h00000200:

// (58) data[2]

ram[5'h17] = 32'hfffffffff:

// (5c) data[3]

// ram[5'h18] the sum stored by sw instruction

end

sc instmem.s.txt

endmodule

```

#### テストベンチ

```

'timescale 1ns/1ns

module sc_computer_tb;

reg clk. clrn:

wire [31:0] inst, pc, aluout, memout;

sc_computer cpu (.clk(clk),

.clrn(clrn),

.instr(inst),

.pc(pc),

.alu(aluout),

.mem(memout));

initial begin

#0 clrn = 0:

#0 clk = 1;

#1 clrn = 1:

#1399 $finish; // 1400 ns

end

always #10 clk = !clk:

initial begin

$dumpfile ("sc_computer.vcd");

$dumpvars:

end

endmodule

```

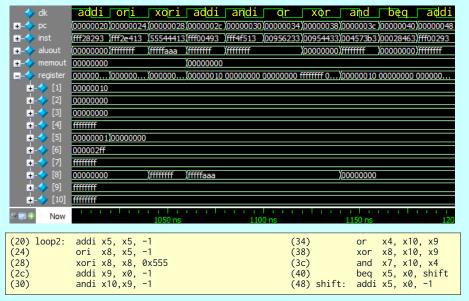

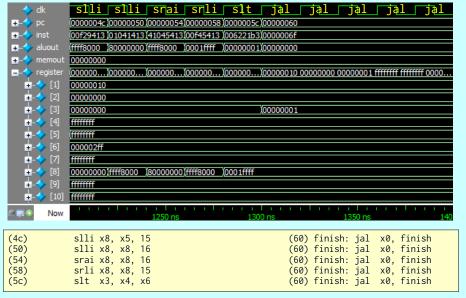

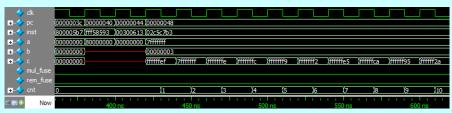

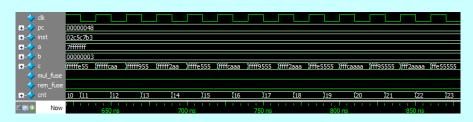

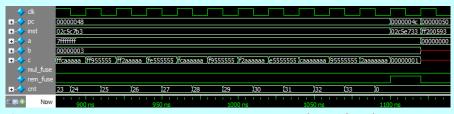

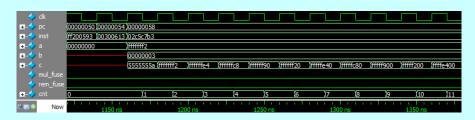

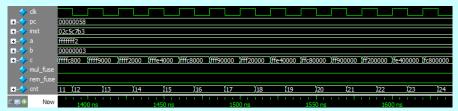

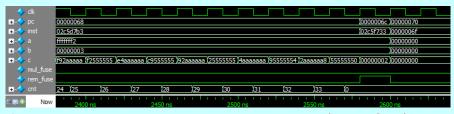

#### レジスタファイルの波形を表示する

- ① In the ModelSim main window, check View ▶ Memory List (w)

- 2 In the ModelSim main window, select the Memory List window

- 3 Drag /sc\_computer\_tb/cpu/.../register and drop it to the Wave window

# レジスタファイルの波形を表示する

#### On Mac PC:

```

iverilog -Wall -o sc_computer sc_computer_tb.v \

sc_computer.v sc_datamem.v sc_instmem.v \

sc_cpu.v dff32.v pc4.v sc_cu.v mux2x32.v alu.v \

regfile.v imme.v mux4x32.v branch_addr.v \

jalr_addr.v jal_addr.v

```

gtkwave sc\_computer.vcd

ターミナルで gtkwave 起動後 SST の sc\_computer\_tb の 左側にある三角形のボタンを押し、表示された cpu を 選択すること...

#### 2進数の乗算

#### 繰り返し乗算アルゴリズム

```

// 積

c = 0 0 0 0 0 0 0 0

// 被乗数 (かけられる数) (14)

a = 0 0 0 0 1 1 1 0

b = 0 0 0 0 1 0 1 0

// 乗数 (かける数) (10)

1. 乗数 b 最下位ビットが 0

C = 0 0 0 0 0 0 0 0

// 積

a = 0 0 0 1 1 1 0 0

// 被乗数を左に1ビットシフトする

// 乗数を右に1ビットシフトする

b = 0 0 0 0 0 1 0 1

2. 乗数 b 最下位ビットが 1

c = c + a = 0 0 0 1 1 1 0 0 // 積

// 被乗数を左に1ビットシフトする

a = 0 0 1 1 1 0 0 0

// 乗数を右に1ビットシフトする

b = 0 0 0 0 0 0 1 0

3. 乗数 b 最下位ビットが 0

// 積

c = 0 0 0 1 1 1 0 0

// 被乗数を左に1ビットシフトする

a = 0 1 1 1 0 0 0 0

b = 0 0 0 0 0 0 0 1

// 乗数を右に1ビットシフトする

4. 乗数 b 最下位ビットが 1

c = c + a = 1 0 0 0 1 1 0 0 // 積 (128+12 = 140 = 14*10)

// 被乗数を左に1ビットシフトする

a = 1 1 1 0 0 0 0 0

// 乗数を右に1ビットシフトする

b = 0 0 0 0 0 0 0 0

```

# 繰り返し乗算アルゴリズム (C 言語)

```

# include <stdio.h>

int mul(int x, int y){

int a, b, c;

11 カウンタ

int i;

// 被乗数 (かけられる数)

a = x;

// 乗数 (かける数)

b = y;

c = 0:

for (i = 0; i < 16; i++) { // 16 回繰り返す:

乗数最下位ビットが 1 ならば

if ((b & 1) == 1) {

//

積 = 積 + 被乗数

c += a:

11

被乗数を左に 1 ビットシフトする

a = a << 1:

乗数を右に 1 ビットシフトする

b = b >> 1;

// 積を返す

return(c):

int main(){

int x = 0xc93f;

int y = 0xe6c7;

printf("0x%08x * 0x%08x = 0x%08x\n", x, y, mul(x, y));

return 0;

```

# 繰り返し乗算アルゴリズム (C 言語)

```

yamin@localhost:/home/yamin/lectures/cod

~/lectures/cod $ cat mul by shift add.c

# include <stdio.h>

int mul(int x, int y){

int a, b, c;

int i;

// カウンタ

// 被乗数 (かけられる数)

a = x;

b = y;

// 乗数 (かける数)

// 秸

c = 0:

for (i = 0; i < 16; i++) { // 16回繰り 返す:

if ((b & 1) == 1) { // 乗数最下位ビットが 1 ならば

c += a;

秸 = 秸 + 被乗数

// 被乗数を左に 1 ビットシフトする

a = a << 1:

b = b >> 1;

乗数を右に 1ドットシフトする

return(c);

// 積を 返す

int main(){

int x = 0xc93f;

int y = 0xe6c7;

printf("0x\%08x * 0x\%08x = 0x\%08x\n", x, y, mul(x, y));

return 0;

~/lectures/cod $ gcc mul_by_shift_add.c -o mul_by_shift_add

~/lectures/cod $ ./mul by shift add

0x0000c93f * 0x0000e6c7 = 0xb56b09f9

~/lectures/cod $

```

## 乗算プログラム

次の乗算プログラムを完成させ、Rivasmに実行させ、Verilog HDLに変換させ、さらに自分の CPU に実行させなさい。

```

.data 0

x: .word 0xc93f, 0xe6c7, 0 # 被乗数, 乗数, 積

.text 0

# (00) data address

main: la x10, x

lw x14, 0(x10) # (04) 被乗数

lw x15, 4(x10) # (08) 乗数

# (0c) 積

mul:

add x16, x0, x0

addi x12, x0, 16

# (10) counter

# (14) 乗数の最下位ビット

loop:

# (18) 0 なら go to shift

(1c) 積 = 積 + 被乗数

# (20) 被乗数をシフト

shift:

# (24) 乗数をシフト

addi x12, x12,-1 # (28) counter - 1

x12, x0, loop # (2c) 条件分岐

x16, 8(x10) # (30) 積をメモリに保存

SW

finish: j

finish

# (34)

.end

```

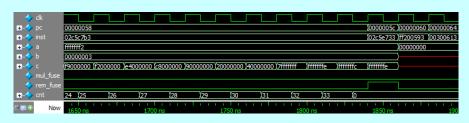

## <u>乗</u>算プログラム

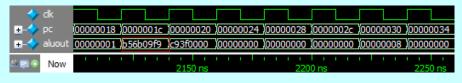

pc = 0x0000001c:  $0xc93f \times 0xe6c7 = 0xb56b09f9$

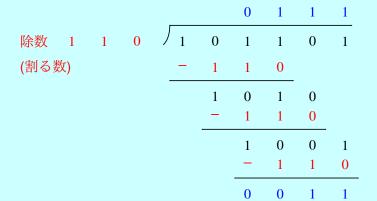

## 2進数の除算

$$45 / 6 = 7 \dots 3$$

商

被除数

(割られる数)

剰余

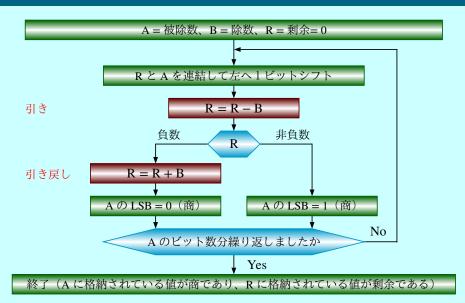

## 除算 — 引き戻し法(符号なし)

## 引き戻し例: A = 1101, B = 0011

| 繰返し回数 | 操作            | 除数   | 剰余    | 被除数,商                |

|-------|---------------|------|-------|----------------------|

|       |               | В    | R     | A                    |

| 0     | 初期化           | 0011 | 00000 | 1101                 |

| 1     | RA を左シフト      | 0011 | 00001 | 101                  |

|       | R = R - B     | 0011 | 11110 | 101                  |

|       | R は負数, 商 0    | 0011 | 11110 | 1 0 1 <mark>0</mark> |

|       | R を元に戻す       | 0011 | 00001 | 1 0 1 <mark>0</mark> |

| 2     | RA を左シフト      | 0011 | 00011 | 010                  |

|       | R = R - B     | 0011 | 00000 | 0 1 <mark>0</mark>   |

|       | R は負数でない, 商 1 | 0011 | 00000 | 0101                 |

| 3     | RA を左シフト      | 0011 | 00000 | 101                  |

|       | R = R - B     | 0011 | 11101 | 101                  |

|       | R は負数, 商 0    | 0011 | 11101 | 1010                 |

|       | R を元に戻す       | 0011 | 00000 | 1010                 |

| 4     | RA を左シフト      | 0011 | 00001 | 010                  |

|       | R = R - B     | 0011 | 11110 | 010                  |

|       | R は負数, 商 0    | 0011 | 11110 | 0100                 |

|       | R を元に戻す       | 0011 | 00001 | 0100                 |

# 除算 — 引き戻し法(符号付き)

```

inputs: signed [31:0] x, y;

if x is negative, a = -x;

if y is negative, b = -y;

do restoring division on a and b to get q and r;

if the signs of x and y are different, q = -q;

if x is negative, r = -r;

```

#### Examples:

$$7 / 2 = 3 \dots 1$$

$7 / -2 = -3 \dots 1$

$-7 / 2 = -3 \dots -1$

$-7 / -2 = 3 \dots -1$

# 除算 — 引き放し法(符号なし)

- 引き戻し法では剰余が負になった場合, R = R + B を実行して 剰余を元に戻す。

- その後に、元に戻した剰余を1ビット左にシフトし、Bを引く。

- これらの操作を次のように簡単にできる: (R+B)×2-B=2R+B

- つまり、剰余が負数の場合、元に戻し、そこからBを引く代わりに、剰余を1ビット左にシフトし、それにBを足すことよっても同じ効果が得られる。

# 引き放し例: A = 1101, B = 0011

| 繰返し回数 | 操作            | 除数       | 剰余    | 被除数,商                |

|-------|---------------|----------|-------|----------------------|

|       |               | В        | R     | A                    |

| 0     | 初期化           | 0011     | 00000 | 1101                 |

| 1     | RA を左シフト      | シフト 0011 |       | 101                  |

|       | R = R - B     | 0011     | 11110 | 101                  |

|       | R は負数, 商 0    | 0011     | 11110 | 1 0 1 <mark>0</mark> |

| 2     | RA を左シフト      | 0011     | 11101 | 010                  |

|       | R = R + B     | 0011     | 00000 | 010                  |

|       | R は負数でない, 商 1 | 0011     | 00000 | 0101                 |

| 3     | RA を左シフト      | 0011     | 00000 | 101                  |

|       | R = R - B     | 0011     | 11101 | 101                  |

|       | R は負数, 商 0    | 0011     | 11101 | 1010                 |

| 4     | RA を左シフト      | 0011     | 11011 | 010                  |

|       | R = R + B     | 0011     | 11110 | 010                  |

|       | R は負数, 商 0    | 0011     | 11110 | 0100                 |

| End   | R は負数, 剰余 +B  | 0011     | 00001 | 0100                 |

# 除算 — 引き放し法(符号付き)

```

inputs: signed [31:0] x, y;

if x is negative, a = -x;

if y is negative, b = -y;

do non-restoring division on a and b to get q and r;

if the signs of x and y are different, q = -q;

if x is negative, r = -r;

Examples:

```

$$7 / 2 = 3 \dots 1$$

$7 / -2 = -3 \dots 1$

$-7 / 2 = -3 \dots -1$

$$-7/-2 = 3 \dots -1$$

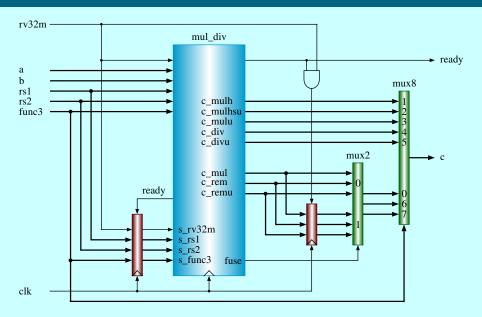

## RV32M (Mul/Div/Rem) Instructions

| 0000001 | rs2 | rs1 | 000 | rd | 0110011 |

|---------|-----|-----|-----|----|---------|

| 0000001 | rs2 | rs1 | 001 | rd | 0110011 |

| 0000001 | rs2 | rs1 | 010 | rd | 0110011 |

| 0000001 | rs2 | rs1 | 011 | rd | 0110011 |

| 0000001 | rs2 | rs1 | 100 | rd | 0110011 |

| 0000001 | rs2 | rs1 | 101 | rd | 0110011 |

| 0000001 | rs2 | rs1 | 110 | rd | 0110011 |

| 0000001 | rs2 | rs1 | 111 | rd | 0110011 |

mul mulhsu mulhu div divu rem remu

```

mul

rd, rs1, rs2

# rd <- rs1 * rs2 (product low, same for signed and unsigned)

mu1h

rd. rs1. rs2

# rd <- rs1 * rs2 (product high of signed * signed)</pre>

mulhsu rd, rs1, rs2

# rd <- rs1 * rs2 (product high of signed * unsigned)</pre>

mulhu rd, rs1, rs2

# rd <- rs1 * rs2 (product high of unsigned * unsigned)</pre>

div

rd, rs1, rs2

# rd <- rs1 / rs2 ( signed)

divu

rd, rs1, rs2

# rd <- rs1 / rs2 (unsigned)

rd, rs1, rs2

# rd <- rs1 % rs2 ( signed)

rem

remu

rd, rs1, rs2

# rd <- rs1 % rs2 (unsigned)

```

#### RISC-V RV32M Fuse

- "If both the high and low bits of the same product are required, then the recommended code sequence is: MULH[[S]U] rdh, rs1, rs2; MUL rdl, rs1, rs2 (source register specifiers must be in same order and rdh cannot be the same as rs1 or rs2). Microarchitectures can then fuse these into a single multiply operation instead of performing two separate multiplies."

- "If both the quotient and remainder are required from the same division, the recommended code sequence is: DIV[U] rdq, rs1, rs2; REM[U] rdr, rs1, rs2 (rdq cannot be the same as rs1 or rs2). Microarchitectures can then fuse these into a single divide operation instead of performing two separate divides."

## RISC-V RV32M Fuse

## RISC-V RV32IM

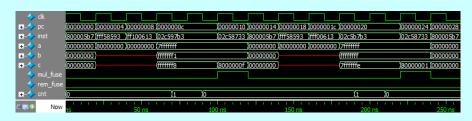

## RISC-V RV32M Test Program

```

.text

main:

li a2, -15 # (08) b

L = 0 \times 80000000 f

mulh a5, a1, a2 # (0c) product high

mul a4, a1, a2 # (10) product low, fused with mulh

li a2, -1 # (1c) b L = 0x80000001

mulhu a5, a1, a2 # (20) product high

mul a4, a1, a2 # (24) product low, fused with mulhu

li a2, -1 # (30) b L = 0x80000001

mulhsu a5, a1, a2 # (34) product high

mul a4, a1, a2 # (38) product low, fused with mulhsu

```

## RISC-V RV32M Test Program

```

sign0: li

a2, 3 # (44) b R = 0x00000001

li

div a5, a1, a2 # (48) div signed

rem a4, a1, a2 # (4c) rem signed, fused with div

a2, 3 # (54) b R = 0xfffffffe

li

a5, a1, a2 # (58) div signed

div

rem a4, a1, a2 # (5c) rem signed, fused with div

li a2, 3 # (64) b R = 0x00000002

divu

a5, a1, a2 # (68) div unsigned

a4, a1, a2 # (6c) rem unsigned, fused with divu

remu

finish: jal x0, finish # (70) dead loop

. end

```

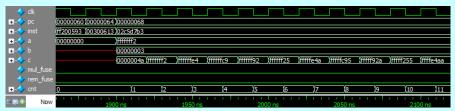

#### mulh-mul: 0xfffffff88000000f; mulhu-mul: 0x7ffffffe80000001

div-rem: 0x7fffffff / 3

#### div-rem: 0x7fffffff / 3

div q = 0x2aaaaaaa, rem r = 0x00000001 (rem fuse)

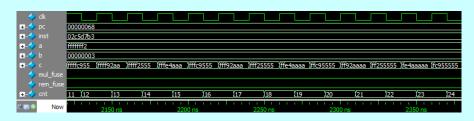

#### div-rem: 0xfffffff2 / 3

div-rem: 0xfffffff2 / 3

#### div q = 0xfffffffc, rem r = 0xfffffffe (rem fuse)

divu-remu: 0xfffffff2 / 3

#### divu-remu: 0xfffffff2 / 3

divu q = 0x55555550, remu r = 0x00000002 (remu fuse)

# 課題 VI (500 点 + 100 点)

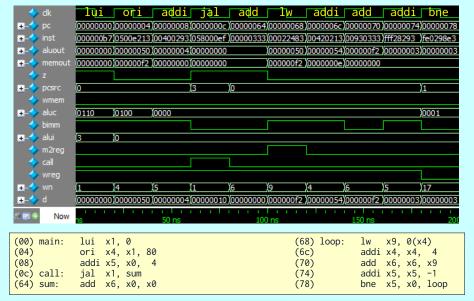

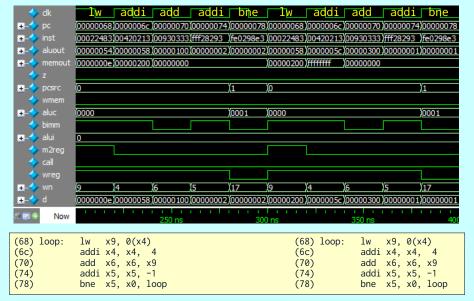

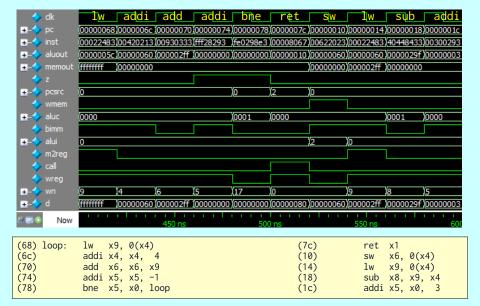

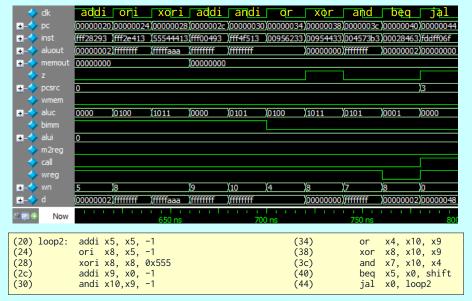

単一サイクルコンピュータ sc\_computer を設計とシミュレーションしなさい。シミュレーション時の出力に関して、どんな命令を実行しているのか、どのような演算がされているかを自分で計算した結果と比較して波形の説明を入れること (500 点)。

オプション (+100 点):

Design and simulate an RISC-V CPU RV32IM that can execute RISC-V integer instructions as well eight multiplication and division instructions (see P47-P57).